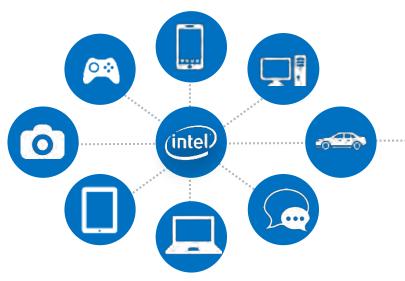

## Internet of Things Group

Lead the industry in transforming businesses and the way we live by making it simple to create exciting, new IoT solutions

SILICON, SOFTWARE AND SECURITY **SCALABILITY**

# WIND RIVER

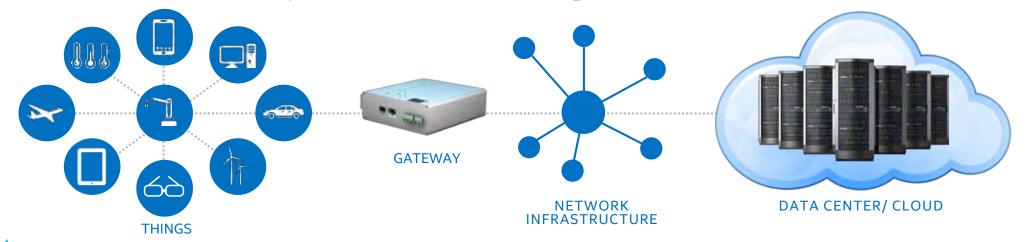

THE INTERNET OF Devices that connect to the Internet THINGS: integrating greater compute capabilities using data analytics to extract information

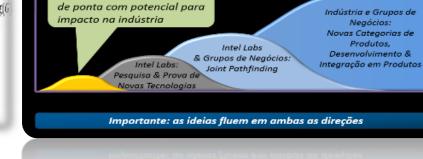

# **INTEL LABS**

Deliver breakthrough innovations to fuel Intel's growth and technology leadership

#### **COLLABORATE FOR RESULTS**

#### **KEY RESEARCH FOCUS AREAS**

USER EXPERIENCE

ARCHITECTURE AND DESIGN

SYSTEMS AND SOFTWARE

SECURITY AND PRIVACY

INTEGRATED COMPUTING

#### **ADDITIONAL ORGANIZATIONS**

STRATEGY, PLANNING and COLLABORATION

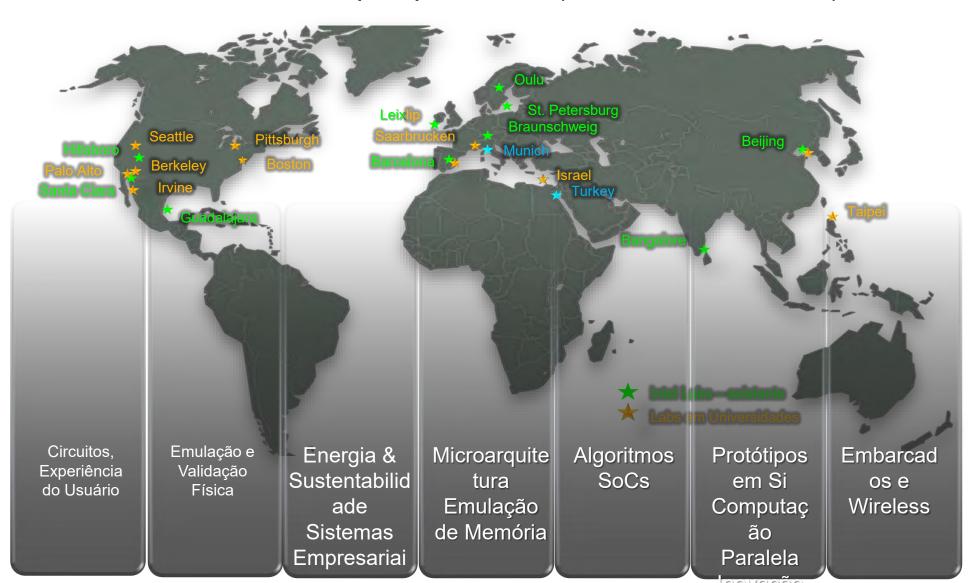

INTEL LABS EUROPE Sustainable Intelligent Systems INTEL LABS CHINA China Tech Ecosystem

# Intel Labs & Conselho de Pesquisa

1.000+ pesquisadores (70% EUA, 30% WW)

### ISRA Brasil – Segurança em SoC com Eficiência Energética

Tema principal: Tecnologias que tornarão os dispositivos em um único chip (SoC) significativamente mais seguros do que os mais avançados atualmente, ainda assim evitando um consumo excessivo de bateria.

2013 workshop - 14 people

Method and Energy-Efficient FPGA-based SoC

Implementation for Anomaly Detection System

Software Implementation of Cryptographic Algorithms

LINICAMP

Energy-Efficient Instrumentation to Secure SoC Devices

Universidades: perspectivas

Universidade da Basilla

$\leftarrow v, G \leftarrow g, B \leftarrow 1, C \leftarrow 0, t \leftarrow \deg(g)$  $\mathsf{vhile}\left(\deg(G) > \lfloor t/2 \rfloor\right) \{$

F ↔ G.B ↔ C

while  $(\deg(F) \ge \deg(G))$  {

$j \leftarrow \deg(F) - \deg(G), h \leftarrow F_{\deg(F)}/G_{\deg(G)}$  $F \leftarrow F - hx^{\dagger}G, B \leftarrow B - hx^{\dagger}C$

$\sigma(x) \leftarrow G(x)^2 + xC(x)^2$

pesquisas de ponta e programas em parceria com

Grupo de Pesquisas com

a Intel, a academia, governos e indústria.

# ISRA Brasil – Alguns Resultados

| Universidade – Escola                                                                                                                                 | Projeto                                                                                         | Papers Publicados                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Universidade de São Paulo (USP) –<br>Laboratório de Arquitetura de Redes de<br>Computadores (LARC)                                                    | Asymmetric Cryptography for<br>Embedded Systems                                                 | <ul> <li>A Parallel and Uniform k-Partition Method for Montgomery Multiplication</li> <li>Optimized and Scalable Quasi-Dyadic Goppa Hardware Encoder and Decoder for Cryptographic Applications</li> <li>Efficient Construction of Quasi-Dyadic Goppa Codes</li> <li>Shorter UOV Signatures</li> </ul>                                                                                                                                                                                                                                                                                            |

| Universidade de Campinas (UNICAMP)  – Instituto de Computação                                                                                         | Software Implementation of Cryptographic Algorithms                                             | <ul> <li>Two is the fastest prime: lambda coordinates for binary elliptic curves</li> <li>Lambda Coordinates for Binary Elliptic Curves</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Universidade Federal de Minas Gerais<br>(UFMG) – Ciência da Computação                                                                                | eCoSoc: Energy-Efficient Instrumentation to Secure SoC Devices                                  | <ul> <li>Aranot - An Array Annotator for C and C++</li> <li>Tool to Detect Vulnerabilities in Code Protected With Canaries</li> <li>Static Array Bounds-Checking in C</li> <li>GreenArrays: Securing Array Access in C</li> <li>GreenArrays: Speeding up Safe C Code via Static Analyses</li> <li>Flow Tracking: An Address Leak Detection System</li> <li>An Intermediary Representation for Implicit Information Leak Detection</li> <li>Software Security for Embedded Systems: Attacks &amp; Countermeasures</li> <li>An Energy Evaluation of Security Tools over Embedded Systems</li> </ul> |

| Universidade de Brasília (UNB) –<br>Engenharia Elétrica                                                                                               | Physical Unclonable Functions for SoC Devices                                                   | <ul> <li>A Framework for Assessing the Use of SoC SRAMs as Physically Unclonable Functions.</li> <li>On the Left-Over Hash Lemma and Smooth Entropies for Infinite Dimensional Distributions</li> <li>Characterization of SRAM cells and their potential for building challenge-response PUFs</li> </ul>                                                                                                                                                                                                                                                                                          |

| Pontifícia Universidade Católica do<br>Paraná + Universidade Federal do<br>Paraná + Universidade Técnica Federal<br>do Paraná – Ciência da Computação | Method and Energy-Efficient<br>FPGA-based SoC<br>Implementation for Anomaly<br>Detection System | <ul> <li>State-of-the art in Anomaly Detection Techniques and FPGA Implementations</li> <li>Signature-based Detection Implemented by an Anomaly-detection Technique</li> <li>Moving Network Protection from Software to Hardware: an Energy Efficiency Analysis.</li> </ul>                                                                                                                                                                                                                                                                                                                       |

## Intel Software & Services Group

SSG enhances computing and connectivity for Intel Architecture across the software ecosystem and through our software products and services.

Network Infrastructure

**Cloud API Services**

**Cloud and Data Center Products**

Client Software Platforms

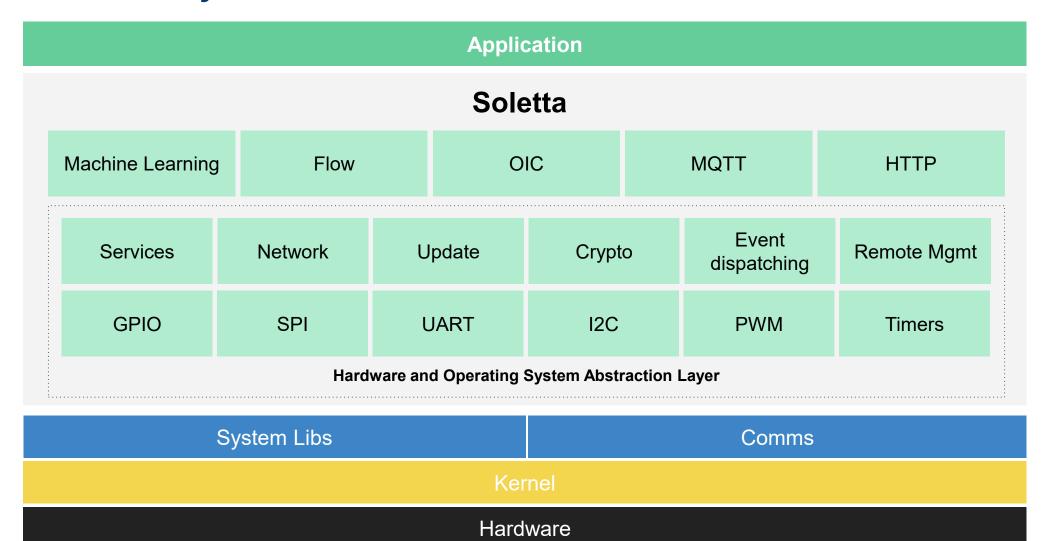

# Soletta Project - solettaproject.org

Soletta is a framework for making IoT devices.

It is **cross-platform**, works with **Linux and small OSes, like Zephyr**, over **different boards**.

**Portable**, abstracts information specific to determined HW and OS, requiring minimum changes to code when flashed to different targets.

#### Available now on github.com/solettaproject

- multi OS: Zephyr, Riot, Contiki, Linux

- platform abstraction

- uniform event loop

- uniform basic I/O primitives

- used as dynamic library, static library or interpreter runtime

- high level programming apis (C/C++, FBP)

- FBP flow-based programming (optional)

- supports OIC, CoAP, MQTT, Bluetooth and HTTP (client and server)

- lightweight (f=flash or disk, r=ram):

RIOT on Arduino Due f=76Kb, r=8.8Kb

Contiki on Intel Curie (CTB) f=65Kb, r=1.8Kb

Linux on Minnow (userspace/PID1) f=88Kb, r=38Kb

easy to use development system

Soletta Framework github.com/solettaproject/soletta

The framework itself and core components.

#### **Soletta Machine Learning**

github.com/solettaproject/soletta-machine-learning

Provides APIs to deal with client side AI and an easy to use flow-based Soletta module. Initially supporting neural networks and fuzzy logic learning.

(Linux-only)

#### **Soletta Development Application**

github.com/solettaproject/soletta-dev-app

Web-based environment running on target board where developers can write, visualize, modify, run, test and debug their Soletta FBP programs.

# Soletta Project – Architecture

### www.intel.com/jobs

Previous Editions

### VI Brazilian Symposium on Computing Systems Engineering

November 01 - 04, 2016 - João Pessoa - Paraíba - Brazil

# MENU Home Scope Organization Paper Submission Call for Papers Deadlines Co-events Registration Keynote Speakers Venue Program Accommodation Proceedings Photo Gallery Login

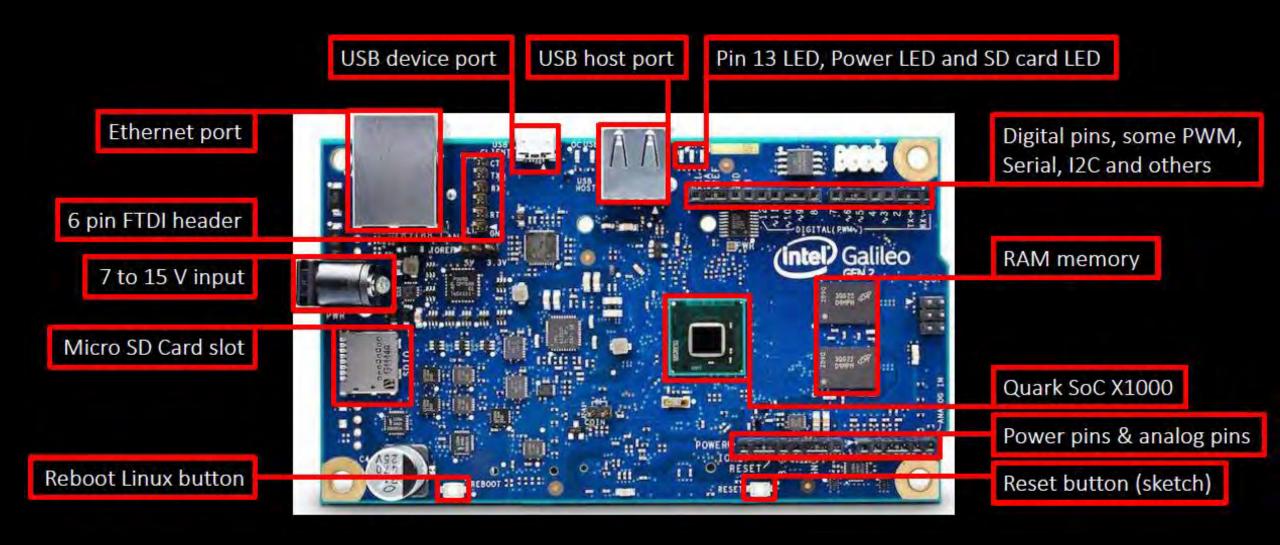

#### Intel® Embedded Systems Competition 2016

The Intel® Embedded Systems Competition 2016 is a competition open to undergraduate and graduate students, providing the opportunity to develop intelligent and innovative Systems and co this segment of Computing in Brazil.

The selected teams will receive Intel® Galileo Gen 2 boards for the project preparation.

During development, each team will have to produce two reports: one "draft" that has to be delivered early and another "final" closer to the end of the project's development. Afterwards, if quali presented at SBESC, which will be held in João Pessoa, Paraíba - Brazil.

#### Competition Regulation

You can find PDF with competition rules here: Competition Regulation 2016

#### Schedule

Submissions: Until April 4

Submission results: April 30

#### First webinars:

Themes: "About the competition" and "About the board" - Join 2

March 07 10h30 March 08 15h00

March 16 - 10h30

March 18 - 15h00

March 28 - 15h00

March 29 - 10h30

BRT - Brasilia (Standard) Time.

Deliver boards to students: Until May 20

#### Technical webinars:

Themes: "Got the board! What next?" and "Technical Q&A"

June 08 - 10h30

June 09 - 15h00

August 23 - 15h00

August 24 - 10h30

BRT - Brasilia (Standard) Time.

First project reports delivery: September 20

Final project reports delivery: October 30

SBESC Event: November 01-04

## **General Information:**

- Open to undergraduate and graduate students

- Opportunity to develop intelligent and innovative Systems

- Work with Intel® technology

- Teams up to 3 students and 1 teacher

- Contact: submissaocompeticaointel@gmail.com

Create an Embedded System contained in at least one of the following areas:

- Smart cars / home / cities

- Health

- Industrial Automation

- Wearables

- Security

- Retail

### **Action Plan:**

- Phase 1: submission and evaluation

- Phase 2: board delivery / first report submission (in Portuguese)

- Phase 3: final report submission (in English) / presentation at VI Brazilian

Symposium on Computing Systems Engineering

# Schedule National Competition:

- April 4<sup>th</sup>: Deadline for submissions

- April 30<sup>th</sup>: Submission results

- March 7<sup>th</sup> to August 24<sup>th</sup>: Webinars\*

- May 20<sup>th</sup>: Deadline for board delivery

- September 20<sup>th</sup>: First project reports delivery

- September 30<sup>th</sup>: Approved groups for phase 3

- October 30<sup>th</sup>: Competitors should deliver the final project report directly at JEMS

- November 1<sup>st</sup> to November 4<sup>th</sup>: SBESC Event / Final Results

<sup>(</sup>intel

# Intel® Galileo (Gen 2)

- 10/100 Mbps Ethernet\* RJ45 port.

- 12 V Power-over-Ethernet capable.

- Serial console UART header is compatible with FTDI USB converters.

- Console UART1 can be redirected to Arduino\* headers in sketches.

- Full-sized mini-PCI Express\* 1x slot.

- Accepts power suppliers from 7V to 15V.

# Intel® Galileo (Gen 2)

- Intel® Quark™ SoC X1000 @ 400MHz

- 32-bit Intel<sup>®</sup> Pentium<sup>®</sup> processorcompatible ISA.

- 16KB L1 cache, 512KB SRAM.

- ACPI-compatible with CPU sleep states.

- RTC with optional 3V coin cell battery.

- 256MB DDR3 DRAM.

- SD Card up to 32GB.

- USB 2.0 host and client ports.

# Intel® Galileo (Gen 2)

# Intel® Higher Education Programs

Investing Over \$670 Million in University Programs Since 2001.

Resources for University Professors

University Student Center

Opportunities for University Researchers

## **Curricula Development**

# Other University Collaborations Contests and Entrepreneurship

Security Curricula >

Parallel Programing

Curricula >

**Embedded University**

Program >

Intel® Galileo Curricula >

Intel® Software Academic

Program >

Strategic Research

Relationships >

Intel Science and Technology

Centers >

Intel Collaborative Research

Institutes >

Focused Research

Collaborations >

Break and Make (Eastern Europe) >

Challenge UP (Europe) >

The Cornell Cup USA >

Innovate Malaysia Design

Competition >

Intel Cup China >

Intel Cup Mexico >

Intel® Global Challenge >

Intel India Embedded Challenge >

National Collegiate Software

Innovation Contest (China) >

Taiwan Embedded

Systems Contest >

Intel® Higher Education Professor Programs

**OVER 115**

The number of U.S. technology curricula developed in conjunction with higher education faculty

### **Online Video Courses**

# **Student Support**

# **Contests and Entrepreneurship**

Parallel Programming > Security / Privacy >

Job Center for Students/Recent

Grads >

Scholarships >

Intel® PhD Fellowship Program >

National Consortium for Graduate

**Degrees for Minorities in**

Engineering & Science (GEM) >

**SRC Graduate Fellowship**

Program (GFP) >

SRC Undergraduate Research

Opportunity (URO) >

Stay With It™ >

Break and Make (Eastern Europe) >

Challenge UP (Europe) >

The Cornell Cup USA >

Innovate Malaysia Design Competition >

Intel Cup China >

Intel Cup Mexico >

<u>Intel® Global Challenge ></u>

Intel India Embedded Challenge 2014 >

National Collegiate Software Innovation

Contest (China) >

<u>Taiwan Embedded Systems Contest ></u>

Intel® Higher Education Student Programs

OVER \$55 MILLION

Amount of dollars Intel has awarded students for fellowships and scholarships in the U.S. since 2001

# https://software.intelscom/en-us/iot/home

Select your device and find guides, documentation, downloads, support, and more.

Intel® Galileo Board >

Intel® IoT Gateways >

Sensors >

Intel® IoT Developer Kit >

**Shared curriculums from**

universities on Intel.com

Subset Academic Programs

# Recommended for Getting Started

Welcome to the Intel® Internet of Things. We offer a variety of online resources to help you get started with your <u>Galileo Boards</u> and <u>Developer Kits</u>. Please visit the links below for more information:

### **Getting Started**

https://software.intel.com/en-us/iot/home

### **Sample Projects**

- http://www.instructables.com/id/intel/

- <a href="https://www.youtube.com/watch?v=qgWGTKzxYwg">https://www.youtube.com/watch?v=qgWGTKzxYwg</a> (Instructions on how to post your project)

- <a href="https://www.hackster.io/intel-edison/projects">https://www.hackster.io/intel-edison/projects</a> (Intel® Edison Boards)

- <a href="https://www.hackster.io/intel-galileo/projects">https://www.hackster.io/intel-galileo/projects</a> (Intel® Galileo Boards)

### **Course Projects and Curriculum**

- https://software.intel.com/en-us/courseware/iot

- https://www-ssl.intel.com/content/www/us/en/education/university/galileo-university-curricula.html

#### **Recommended Books**

- Intel Galileo and Intel Galileo Gen 2: API Features and Arduino Projects for Linux Programmers

- Getting Started with Intel Galileo

- Intel Galileo Gen 2 and Intel Edison for Beginners: A Hands-on Introduction