# UNIVERSIDADE FEDERAL RURAL DO SEMI-ÁRIDO UNIVERSIDADE DO ESTADO DO RIO GRANDE DO NORTE PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO DISSERTAÇÃO DE MESTRADO EM CIÊNCIA DA COMPUTAÇÃO

Dênis Freire Lopes Nunes

ESTENDENDO O CONJUNTO DE INSTRUÇÕES DA IPNOSYS PARA IMPLEMENTAÇÃO DE SOFTWARE *PIPELINING*

# Dênis Freire Lopes Nunes

# ESTENDENDO O CONJUNTO DE INSTRUÇÕES DA IPNOSYS PARA IMPLEMENTAÇÃO DE SOFTWARE *PIPELINING*

Dissertação apresentada ao Mestrado em Ciência da Computação do Programa de Pós-Graduação em Ciência da Computação da Universidade Federal Rural do Semi-Árido e Universidade do Estado do Rio Grande do Norte como requisito para obtenção do título de Mestre em Ciência da Computação.

Linha de Pesquisa: Projeto de Sistemas e Circuitos

Orientador: Silvio Roberto F. de Araújo, Prof. Dr.

Coorientador: Leonardo Augusto Casillo, Prof. Dr. © Todos os direitos estão reservados a Universidade Federal Rural do Semi-Árido. O conteúdo desta obra é de inteira responsabilidade do(a) autor(a), sendo o mesmo, passível de sanções administrativas ou penais, caso sejam infringidas as leis que regulamentam a Propriedade Intelectual, respectivamente, Patentes: Lei nº 9.279/1996, e Direitos Autorais Lei nº 9.610/1998. O conteúdo desta obra tomar-se-á de domínio publico após a data da defesa e homologação da sua respectiva ata. A mesma poderá servir de base literária para novas pesquisas, desde que a obra e seu(a) respectivo(a) autor(a) sejam devidamente citados e mencionados os seus créditos bibliográficos.

#### Dados Internacionais de Catalogação na Publicação (CIP) BIBLIOTECA CENTRAL ORLANDO TEIXEIRA - CAMPUS MOSSORÓ Setor de Informação e Referência

N972e Nunes, Denis Freire Lopes.

Estendendo o conjunto de instruções da IPNoSys para implementação de software pipelining / Denis Freire Lopes Nunes. - Mossoró, 2016. 96f: il.

Orientador: Prof. Dr. Silvio Roberto Fernandes de Araújo Co-Orientador: Prof. Dr. Leonardo Augusto Casillo

Dissertação (MESTRADO EM CIÊNCIA DA COMPUTAÇÃO) - Universidade Federal Rural do Semi-Árido. Pró-Reitoria de Pesquisa e Pós-Graduação

1. Arquitetura de computadores. 2. IPNoSys. 3. Software pipelining. I. Título

RN/UFERSA/BOT/050

CDD 004.22

#### Dênis Freire Lopes Nunes

# ESTENDENDO O CONJUNTO DE INSTRUÇÕES DA IPNOSYS PARA IMPLEMENTAÇÃO DE SOFTWARE *PIPELINING*

Dissertação apresentada ao Mestrado em Ciência da Computação do Programa de Pós-Graduação em Ciência da Computação da Universidade Federal Rural do Semi-Árido como requisito para obtenção do título de Mestre em Ciência da Computação.

Linha de Pesquisa: Projeto de Sistemas e Circuitos

Defendida em: <u>25</u> / <u>02</u> / <u>2016</u>.

Silvio Roberto Fernandes de Araújo, Prof. Dr. (UFERSA)

Orientador

Leonardo Augusto Casillo, Prof. Dr. (UFERSA)

Coorientador

Karla Darlene Napumocemo Ramos, Prof.<sup>a</sup> Dr. <sup>a</sup> (UERN)

Membro Interno

Márcio Eduardo Kreutz, Prof. Dr. (UFRN - DIMAp)

Membro Externo

#### **AGRADECIMENTOS**

Primeiramente a minha família, em nome da minha mãe. Que em tudo me guia para ser a pessoa que sou hoje. Que sempre se sacrificou para que eu pudesse ter um futuro melhor que o dela. Se eu consegui chegar até aqui, é crédito dela.

Ao meu orientador, Prof. Silvio. Que por diversas vezes sentou comigo e "colocou a mão na massa" para debugar código e resolver erros. Acredito que eu tenha ganhado um novo amigo nessa jordana acadêmica. Espero poder compartilhar de outros açaís no futuro.

Ao meu mestre e que me iniciou na paixão pelo hardware. Talvez ele nem saiba a importância que teve no início dessa jornada. Muito obrigado por tudo, Prof. Leonardo Casillo! A cada vez que você perguntava "E aí? Cadê o texto?" eu corria mais pra terminar.

A família LAACOSTE. Principalmente a Álamo e Juliene. Que dividiram esses anos de trabalhos<del>, sofrimento</del> e aprendizagem. Muito sucesso para vocês, amigos!

Por fim, aos amigos que torceram por mim. Que me incentivam com palavras de apoio. Que estiveram ao meu lado durante esse percurso. Fábio, Kelânia, Alysson e Rodolfo, não sei como agradecer a tudo que fizeram por mim. E Eriana Rebouças, queria saber colocar em palavras o quanto eu estou agradecido por tudo que tem me feito. Meu muito obrigado!

"Computadores são servos excelentes e eficientes, mas eu não tenho nenhum desejo de servir a eles."

> Mr. Spock Star Trek: The Original Series S02E24: "The Ultimate Computer"

#### **RESUMO**

A evolução das arquiteturas de computadores está convergindo no sentido de melhorar o desempenho das aplicações por meio do paralelismo. Foi nesse contexto que surgiu a IPNoSys. Esta arquitetura foi baseada em NoC, o que garante um bom cenário para execução paralela. Contudo, ela ainda foi pouco explorada em paralelismo em nível de instrução. Este trabalho teve como objetivo criar instruções, para a ISA da IPNoSys, que irão proporcionar a paralelização de aplicações que contenham laços de repetição através da técnica de software *pipelining*. Esta técnica visa dividir instruções, que estejam dentro de laços de repetição, entre os núcleos disponíveis. Depois de implementada, a nova IPNoSys com software *pipelining* mostrou, que é possível ter uma aceleração superior à dez vezes em aplicações com instruções lógicas e aritméticas, e superior a três vezes em aplicações com acesso memória.

Palavras-chave: Software Pipelining; IPNoSys; Paralelismo em Nível de Instrução

#### **ABSTRACT**

The evolution of computer architectures are converging to improve applications performance by means off parallelism. It was in this context that the IPNoSys was created. This architecture was based on NoC, which ensures a good scenario for parallel execution. However, it was still little explored in instruction level parallelism. This work aimed to create instructions, to the IPNoSys' ISA, which will provide parallelization of applications that containing repeating loops through software pipelining technique. This technique aims to divide instructions, which are within repetition of ties between the available cores. After implemented, the new IPNoSys with pipelining software showed that it is possible to have a higher acceleration to ten times in applications with logical and arithmetic instructions, and more than three times in applications with memory access.

**Keywords:** Software pipelining; IPNoSys; Instruction Level Parallelism

# LISTA DE FIGURAS

| Figura 1 - Produção de CPU's Intel© entre 1970 e 2010                              | 19 |

|------------------------------------------------------------------------------------|----|

| Figura 2 - Classificação de Arquiteturas Paralelas Segundo Flynn                   | 20 |

| Figura 3 - Estruturas de Interconexão: (a) ponto-a-ponto; (b) barramento           | 22 |

| Figura 4 - Modelo de uma NoC                                                       | 23 |

| Figura 5 - Exemplo de execução de instruções em uma arquitetura sem pipeline       | 25 |

| Figura 6 - Exemplo de execução de instruções em uma arquitetura com pipeline       | 25 |

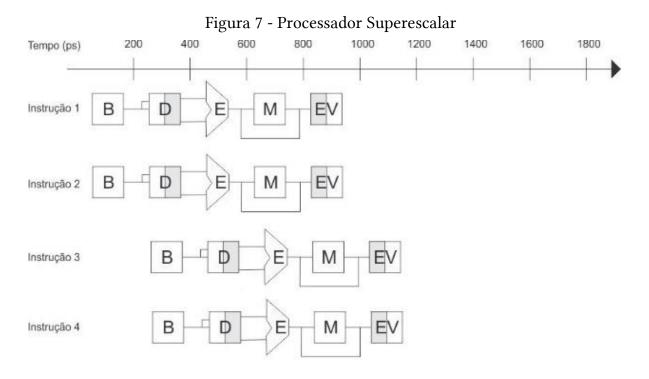

| Figura 7 - Processador Superescalar                                                | 27 |

| Figura 8 - Exemplo de Laço de Repetição                                            | 28 |

| Figura 9 - Execução Sequencial do Algoritmo Exemplo                                | 29 |

| Figura 10 - Execução do Algoritmo com Software <i>pipelining</i> (Ciclos/Iteração) | 29 |

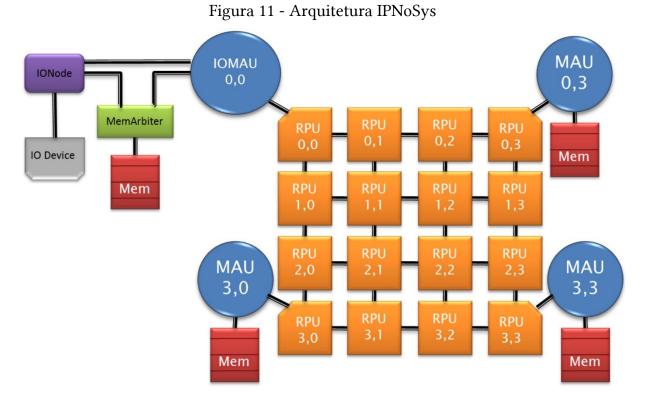

| Figura 11 - Arquitetura IPNoSys                                                    | 30 |

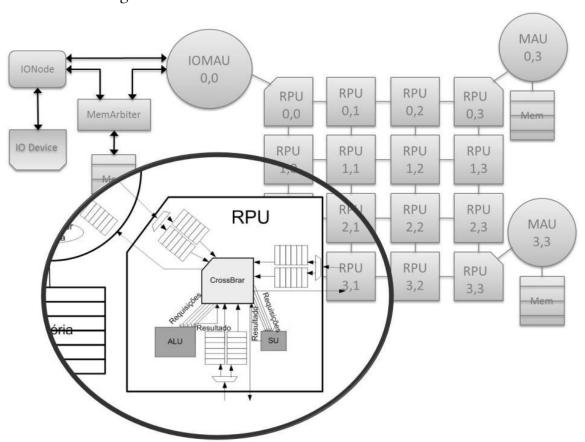

| Figura 12 - Unidade de Processamento e Roteamento                                  | 32 |

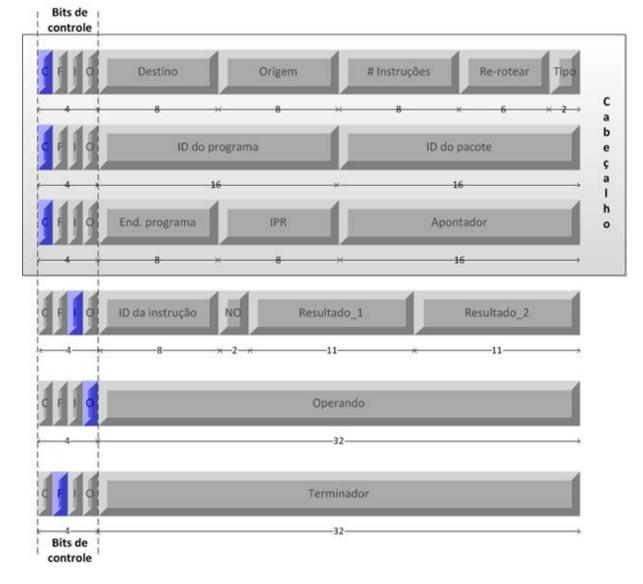

| Figura 13 - Formato do pacote IPNoSys                                              | 34 |

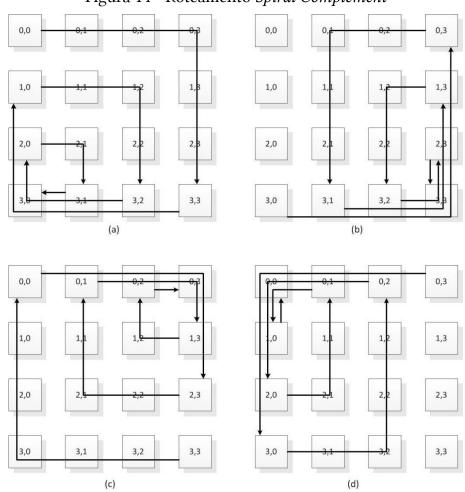

| Figura 14 - Roteamento Spiral Complement                                           | 36 |

| Figura 15 - Roteamento XY                                                          | 37 |

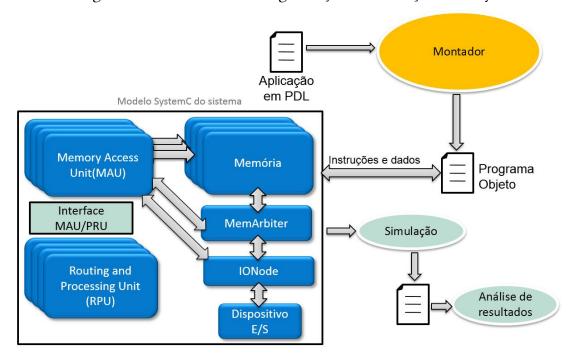

| Figura 16 - Ambiente de Programação e Simulação IPNoSys                            | 39 |

| Figura 17 - Formato de Pacote Modificado Para Software <i>Pipelining</i>           | 41 |

| Figura 18 - Laço de Repetição Tradicional no IPNoSys                               | 44 |

| Figura 19 - PDL da Instrução LOOP (a) e formato da palavra (b)                     | 45 |

| Figura 20 - LOOP Exemplo 01                                                        | 46 |

| Figura 21 - Exemplo de Laço de Repetição Com Dependência de Dados                  | 46 |

| Figura 22 - Palavras da Instrução RT do árbitro para SU                            | 47 |

| Figura 23 - Pacote de Controle com a Função RT                                     | 48 |

| Figura 24 - Algoritmo de Execução do LOOP50                                 |

|-----------------------------------------------------------------------------|

| Figura 25 - PDL de um Laço de Repetição na IPNoSys Original                 |

| Figura 26 - PDL de um Laço de Rpetição na IPNoSys SP                        |

| Figura 27 - Algoritmo de Fatorial                                           |

| Figura 28 - PDL de um Fatorial                                              |

| Figura 29 - Execução Hipotética com IPR = 2                                 |

| Figura 30 - Execução com IPR = 2                                            |

| Figura 31 - Execução com IPR_LOOP = 2                                       |

| Figura 32 - Dependências de Dados Dentro do LOOP                            |

| Figura 33 - Dependência de Dados do Tipo A                                  |

| Figura 34 - Dependência de Dados do Tipo B                                  |

| Figura 35 - Dependência de Dados do Tipo C61                                |

| Figura 36 - Laço de Repetição Com Dependência de Dados Tipo "C"61           |

| Figura 37 - Pipeline Preenchido                                             |

| Figura 38 - Algoritmo Tratamento de Dependências de Dados                   |

| Figura 39 - Bolhas no Software <i>Pipelining</i>                            |

| Figura 40 - Portas no caminho do <i>Spiral Complement</i>                   |

| Figura 41 - IPNoSys IDE                                                     |

| Figura 42 - Procedimento da instrução LOAD (a) atual e (b) a ser proposto85 |

| Figura 43 - Proposta para Nova Palavra de Instrução                         |

# LISTA DE TABELAS

| Tabela 1 - Conjunto de Instrução da IPNoSys                                | . 38 |

|----------------------------------------------------------------------------|------|

| Tabela 2 - Instruções LOOP e RT                                            | . 44 |

| Tabela 3 - Tabela de predição de RPU e porta                               | . 65 |

| Tabela 4 - Relação de Ciclos de <i>Clock</i> IPNoSys SP <i>vs</i> Original | . 67 |

# LISTA DE GRÁFICOS

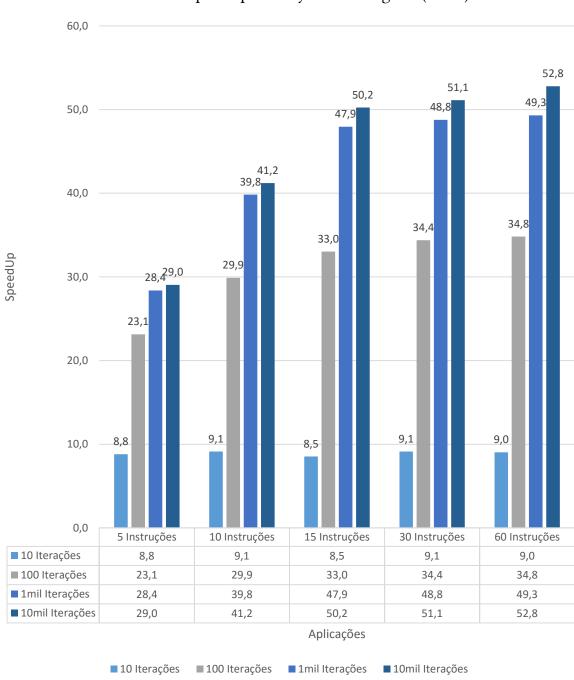

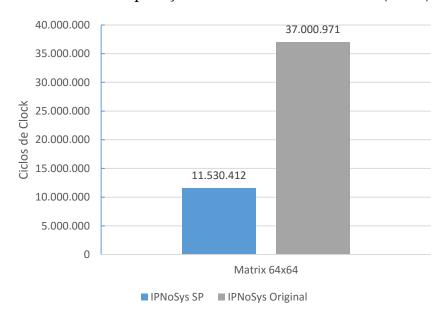

| Gráfico 1 – SpeedUp IPNoSys SP <i>vs</i> Original ( <i>Clock</i> )68                  |

|---------------------------------------------------------------------------------------|

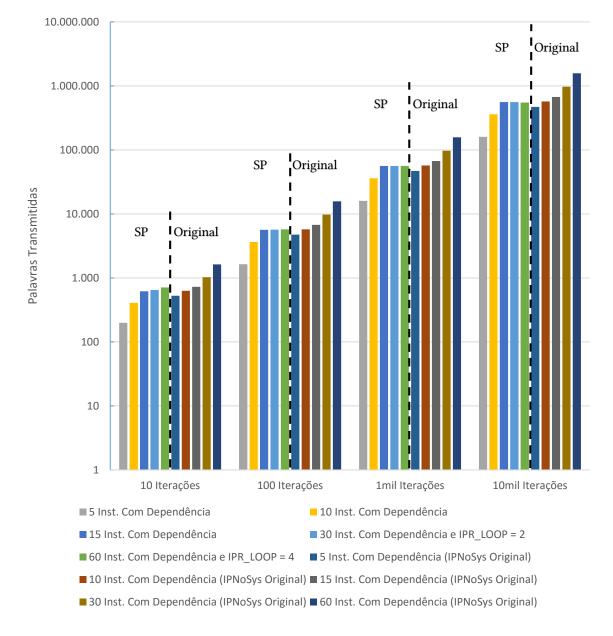

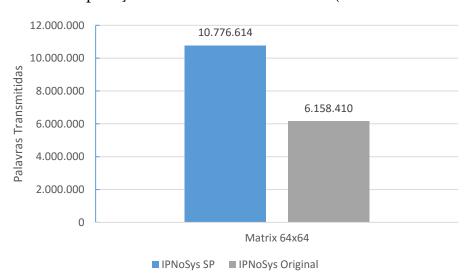

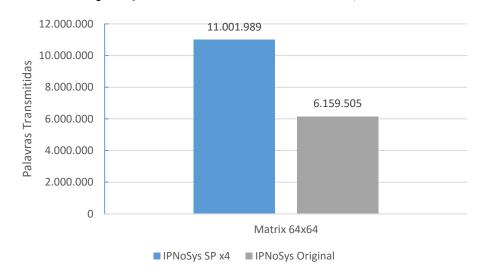

| Gráfico 2 – IPNoSys SP <i>vs</i> Original (Transmissão de Palavras)70                 |

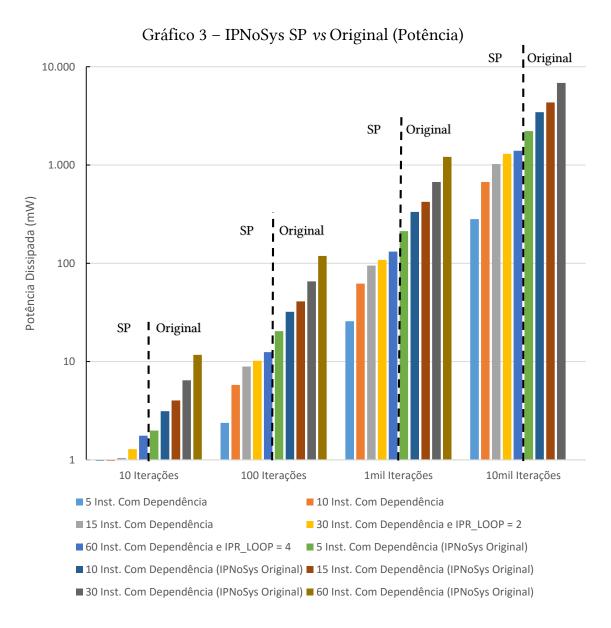

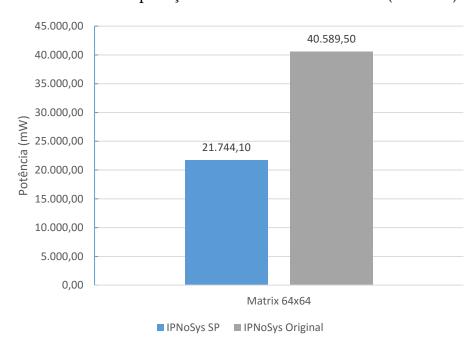

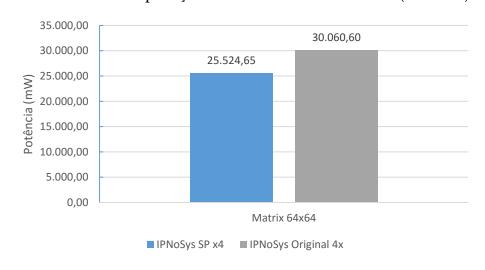

| Gráfico 3 – IPNoSys SP <i>vs</i> Original (Potência)71                                |

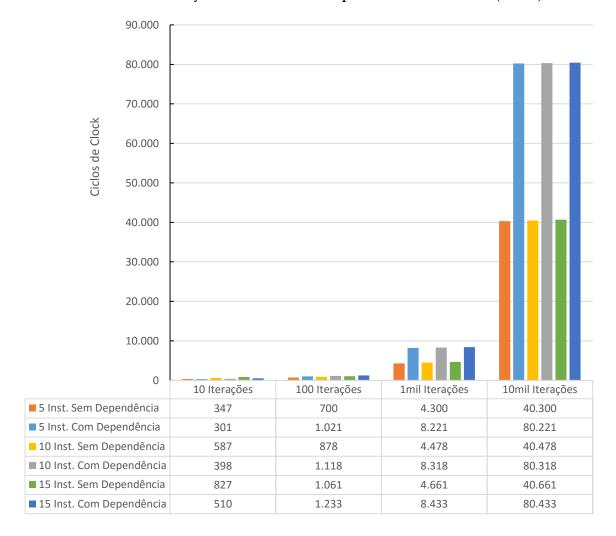

| Gráfico 4 – IPNoSys SP Com <i>vs</i> Sem Dependências de Dados ( <i>Clock</i> )73     |

| Gráfico 5 – IPNoSys SP Com <i>vs</i> Sem Dependências (Transmissão de Palavras)74     |

| Gráfico 6 – IPNoSys SP Com <i>vs</i> Sem Dependências (Potência)75                    |

| Gráfico 7 – Multiplicação de Matrizes com 1 <i>Thread (Clock)</i> 77                  |

| Gráfico 8 – Multiplicação de Matrizes com 1 <i>Thread</i> (Palavras Transmitidas)     |

| Gráfico 9 – Multiplicação de Matrizes com 1 <i>Thread</i> (Potência)79                |

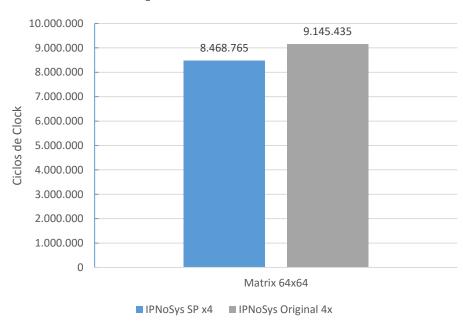

| Gráfico 10 – Multiplicação de Matrizes com 4 <i>Threads</i> ( <i>Clock</i> )80        |

| Gráfico 11 – Multiplicação de Matrizes com 4 <i>Threads</i> (Palavras Transmitidas)81 |

| Gráfico 12 – Multiplicação de Matrizes com 4 <i>Threads</i> (Potência)81              |

#### LISTA DE ABREVIATURAS E SIGLAS

CISC Complex Instruction Set Computer

DLP Data-Level Paralelismo

E/S Entrada e Saída

ILP Instruction-Level Paralelism

IP Intelectual Property

IPR Instruction per RPU

IPNoSys Integrated Processing NoC System

ISA Instruction Set Architecture

MAU Memory Access Unit

MIMD Multiple Instruiction Multiple Data

MIPS Microprocessor Without Interlocked Pipeline Stages

MISD Multiple Instruction Single Data

MPSoC MultiProcessor System-on-Chip

mW Miliwatt

NoC Network-on-Chip

PDL Package Description Language

RISC Reduced Instruction Set Computer

RPU Routing and Processing Unit

SIMD Single Instruction Multiple Data

SISD Single Instruction Single Data

SOC System-on-Chip

SP Software *Pipelining*

SU Synchronization Unit

TLP Thread-Level Paralelism

UC Unidade de Controle

ULA Unidade Lógica e Aritmética

VLIW Very Long Instruction Word

# **SUMÁRIO**

| 1     | INTRODUÇÃO                                 | 15 |

|-------|--------------------------------------------|----|

| 1.1   | Motivação                                  | 16 |

| 1.2   | Objetivos                                  | 17 |

| 1.3   | Organização Desse Trabalho                 | 17 |

| 2     | FUNDAMENTAÇÃO TEÓRICA                      | 18 |

| 2.1   | Processamento Paralelo                     | 18 |

| 2.1.1 | Sistemas em Chip                           | 22 |

| 2.1.2 | Redes em Chip                              | 22 |

| 2.2   | Pipeline                                   | 24 |

| 2.3   | Software Pipelining                        | 27 |

| 2.4   | IPNoSys                                    | 30 |

| 2.4.1 | Visão Geral                                | 30 |

| 2.4.2 | Unidade de Roteamento e Processamento      | 32 |

| 2.4.3 | Formato do Pacote                          | 33 |

| 2.4.4 | Roteamento                                 | 35 |

| 2.4.5 | Programabilidade                           | 37 |

| 2.5   | Trabalhos Relacionados                     | 40 |

| 2.5.1 | Software Pipelining e IPNoSys              | 40 |

| 3     | SOFTWARE PIPELINING NA IPNOSYS             | 43 |

| 3.1   | Visão Geral                                | 44 |

| 3.1.1 | Instrução LOOP                             | 45 |

| 3.1.2 | Instrução RT                               | 46 |

| 3.2   | Implementação                              | 49 |

| 3.2.1 | Definindo o Laço de Repetição              | 49 |

| 3.2.2 | Dependência de Dados                       | 57 |

| 4     | RESULTADOS OBTIDOS                         | 66 |

| 4.1   | IPNoSys SP vs IPNoSys Original             | 67 |

| 4.2   | IPNoSys SP Com e Sem Dependências de dados | 72 |

| 4.3   | Multiplicação de Matrizes                       | 76 |

|-------|-------------------------------------------------|----|

| 4.3.1 | Multiplicação de Matrizes com 1 thread          | 77 |

| 4.3.2 | Multiplicação de Matrizes com 4 threads         | 79 |

| 5     | CONSIDERAÇÕES FINAIS                            | 83 |

| 5.1   | Trabalhos Futuros                               | 84 |

| REFE  | RÊNCIAS                                         | 88 |

| APÊN  | NDICE A – PDL DO FATORIAL UTILIZANDO LAÇO COMUM | 93 |

| APÊN  | NDICE B – PDL DA MULT. DE MATRIZES COM 1 THREAD | 95 |

# 1 INTRODUÇÃO

Desde a década de 70, as arquiteturas de computadores iniciaram uma corrida para acompanhar a crescente demanda de processamento das aplicações (DE ROSE; NAVAUX, 2003). Arquiteturas e técnicas de processamento paralelo começaram, então, cada vez mais, a serem exploradas no intuito de manter a evolução no desempenho. Projetos de computadores com mais de uma unidade funcional foram sendo desenvolvidos. Hoje, arquiteturas multicores e multicomputadores já são presentes em dispositivos domésticos.

Com os avanços tecnológicos na fabricação de circuitos integrados, também foi possível miniaturizar componentes. Essa tecnologia possibilitou inserir vários componentes como processador, memória, dispositivos de entrada e saída em um único chip. Essas arquiteturas foram denominadas de sistemas-em-chip (SoC). A colocação de mais processadores, interligados por um sistema de comunicação, em um SoC, deu origem a um tipo especial de arquitetura chamada de sistemas-em-chip multiprocessados (MPSoCs). Fazer a comunicação de núcleos processantes dentro dos MPSoCs é um dos desafios encontrados pelos projetistas. A transmissão de mensagens pode gerar gargalos e prejudicar o desempenho.

Uma proposta para interconexão em MPSoCs é a rede-em-chip (NoC) (BENINI; DE MICHELI, 2002). O funcionamento das NoCs faz uma analogia às redes de computadores convencionais. Os núcleos processantes são conectados a roteadores e estes, a enlaces. Esse modelo integra uma alta escalabilidade com a possibilidade de transmissão de mensagens em paralelo. As NoCs podem ser configuradas para trabalhar com diversos algoritmos de roteamento, topologias, tipo de chaveamento de mensagens, controle de fluxo, etc.

O trabalho de Araújo (2012) apresentou um novo modelo de NoC, intitulado de *Integrated Processing* NoC *System*, IPNoSys. Esta arquitetura trouxe um novo componente que uniu processadores e roteadores em um único elemento chamado de RPU (Unidade de processamento e Roteamento). Esta arquitetura dispõe de um alto poder de processamento quando comparada às arquiteturas semelhantes, principalmente no processamento de aplicações com alta capacidade de paralelização.

Na IPNoSys, é possível explorar o paralelismo em nível de instrução (ILP) e thread (TLP), entretanto, o modelo de computação atual tira melhor proveio do TLP.

Uma das técnicas para prover paralelismo em nível de instrução é a software *pipelining*, que objetiva a execução simultânea de instruções que compõem um laço de repetição. Este trabalho visa a implementação de técnicas de paralelismo em nível de instrução na arquitetura IPNoSys, a fim de possibilitar um aumento de desempenho na execução de aplicações.

# 1.1 Motivação

O número de trabalhos publicados mostra que a arquitetura IPNoSys vem ganhando destaque no meio acadêmico. No entanto, ela ainda foi pouco explorada em certos aspectos, como no paralelismo em nível de instrução. Como uma NoC, a IPNoSys apresenta um excelente cenário para aplicações paralelas. Contudo, o modelo atual de programação favorece o paralelismo em nível de *thread*.

Como será visto na seção 2.4, cada elemento processante da IPNoSys atua apenas sobre uma instrução do pacote. Isso faz com que os núcleos passem mais tempo transmitindo do que processando. Esse ambiente pode ser modificado para se ajustar a técnica de software *pipelining* de modo aumentar a granularidade do paralelismo e diminuir o tempo de ociosidade dos núcleos.

Criar possibilidade de paralelizar laços pode trazer um aumento de desempenho, principalmente em aplicações com complexidade na ordem de  $O(n^2)$  ou superior. Nessas aplicações grande parte do tempo gasto é originado dos laços de repetição (CORMEN et al, 2002).

A motivação deste trabalho é contribuir com o projeto IPNoSys implementando, na arquitetura, recursos que possam prover novas formas de paralelismo em nível de instrução, através da técnica de software *pipelining*.

# 1.2 Objetivos

O objetivo geral deste trabalho consiste na implementação de uma técnica de paralelismo que visa melhorar o desempenho de aplicações que contenham laços de repetição na rede em chip IPNoSyS. Para isso, será considerada a técnica do software *pipelining*, a qual irá criar um modelo de execução que permita utilizar os recursos da arquitetura para exploração de paralelismo em nível de instruções.

Os objetivos específicos são de criar novas instruções para implementar a técnica de software *pipelining* e manter total compatibilidade com os programas da versão original da IPNoSys (sem software *pipelining*).

Ao final desse trabalho, o desempenho em aplicações que apresentem laços de repetição deve ser melhorado de forma significativa devido a exploração de software *pipelining*.

#### 1.3 Organização Desse Trabalho

Este texto está dividido da seguinte forma: no Capítulo 2, é feita uma revisão bibliográfica sobre arquiteturas paralelas e técnicas de paralelismo, sendo apresentadas as técnicas de *pipeline* e software *pipelining*, além da arquitetura IPNoSys, utilizada no caso de estudos deste trabalho.

No Capítulo 2.5, um breve resumo de alguns trabalhos relacionados, com ênfase em uma implementação anterior de software *pipelining* para IPNoSys.

No Capítulo 3, é apresentada a implementação da técnica de software *pipelining* na IPNoSys desta dissertação.

Em seguida, tem-se os testes executados e os resultados obtidos. E, por último, as considerações finais e as referências utilizadas.

# 2 FUNDAMENTAÇÃO TEÓRICA

Neste capítulo são abordados temas relevantes para este trabalho. A princípio, será feita uma definição sobre técnicas e arquiteturas paralelas. A seguir, será apresentada a arquitetura alvo utilizada como base para desenvolvimento da aplicação descrita por este trabalho. E, por fim, uma explanação sobre a técnica de software *pipelining*.

#### 2.1 Processamento Paralelo

Em meados de 1950, Von Neumann idealizou o primeiro protótipo de um computador de propósito geral. Essa máquina continha uma memória principal, que armazena dados e instruções, uma unidade lógica e aritmética (ULA), uma unidade de controle (UC) e um equipamento de entrada e saída. A unidade de controle operava juntamente com um conjunto de instruções. As instruções são sequências de bits que informam à unidade de controle que operação a ULA irá executar e quais os dados que serão utilizados.

Na medida em que os computadores popularizaram-se, novas operações foram adicionadas ao conjunto de instruções, assim criando os chamados Computadores com um Conjunto de Instrução Complexo (*Complex Instruction Set Computer* – CISC). Segundo Tanenbaum (2013), os microprocessadores CISC se tornaram muito versáteis na execução de aplicações, pois seu grande conjunto de instruções facilita a programação. No entanto, a grande quantidade de instruções do CISC tornou-se inconveniente para várias aplicações mais específicas que precisavam apenas de algumas poucas instruções.

Com uma quantidade reduzida de instruções, os processadores do tipo RISC (Reduced Instruction Set Computer ou Computador com um Conjunto Reduzido de Instruções) apostaram na ideia de que instruções mais complexas podem ser efetuadas a partir do conjunto de outras instruções mais simples. Dessa forma, com poucas instruções, a unidade de controle do processador torna mais simples e a velocidade de execução de cada instrução se torna mais rápida. No cenário atual, Calazans (2008)

afirma que muitas arquiteturas são consideradas híbridas, por possuírem características tanto CISC como RISC.

Com a evolução, os computadores têm sido contemplados pelo aumento na velocidade do processador, diminuição no tamanho dos componentes, aumento no tamanho da memória e aumento da velocidade de entrada e saída (STALLINGS, 2013). Entretanto, desde a década passada, os avanços tecnológicos e evolução das aplicações levaram os microprocessadores a se aproximar de um limiar de velocidade de processamento (*clock*), devido às restrições físicas do aumento de temperatura e consumo de energia.

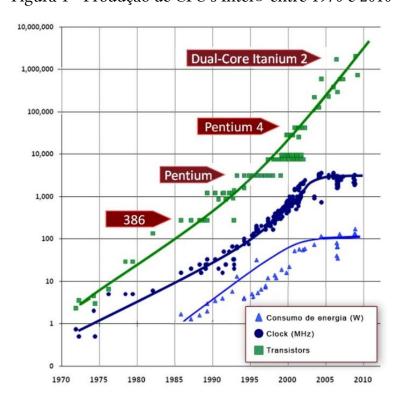

Em contrapartida, à estagnação da velocidade do *clock*, o número de transistores num chip de silício continua aumentando e obedecendo à Lei de Moore (MOORE, 1965). A Figura 1, retirada de Sutter (2005), mostra essa evolução nos processadores da Intel Corporation©.

Figura 1 - Produção de CPU's Intel© entre 1970 e 2010

Fonte: Adaptado de Sutter (2005)<sup>1</sup>

.

<sup>&</sup>lt;sup>1</sup> Apesar da fonte datar de 2005, a figura foi atualizada em 2009 na página on-line do artigo.

Na curva superior, no gráfico da Figura 1, é possível ver a evolução sempre crescente do número de transistores dentro de um chip e na curva do meio, em azul, a evolução da taxa de frequência do *clock*. É possível perceber que os transistores continuam crescendo quase linearmente, enquanto a frequência do *clock* se estabilizou por volta do ano de 2005. Como o consumo de energia tem como um dos fatores a velocidade processamento, a curva do consumo de energia (azul claro) acompanha o do *clock*.

Como aumentar a frequência do *clock* faz o aquecimento e o consumo de energia aumentarem numa proporção maior (TORRES, 2013), a solução encontrada para ampliar o desempenho foi projetar arquiteturas que conseguissem executar mais instruções sem aumentar a velocidade do *clock*. Isso foi possível fazendo duas instruções ou mais, ou partes delas, serem executadas ao mesmo tempo, em paralelo. É importante ressaltar que, nas arquiteturas paralelas, o tempo de execução individual das instruções não é menor. Mas como há execução paralela, duas ou mais instruções são executadas numa mesma unidade de tempo, diminuindo assim a vazão de execução de instruções em um programa.

A ideia de processamento paralelo não é recente. Os trabalhos de Flynn (1966) e Flynn (1972) já descreviam modelos de arquiteturas paralelas. Nesses artigos, Flynn descreveu quatro categorias de máquinas que são aceitas até hoje como a melhor classificação para arquiteturas paralelas. São elas: Single Instruction Single Data (SISD), Single Instruction Multiple Data (SIMD), Multiple Instruction Multiple Data (MIMD), Multiple Instruction Single Data (MIMD),

Único Dados

Unica Instrução

Múltiplos Dados

MISD

Múltiplas Instruções

SIMD

MISD

Figura 2 - Classificação de Arquiteturas Paralelas Segundo Flynn

Fonte: Adaptado de <a href="http://www-usr.inf.ufsm.br/~sandro/elc139/tarefa1.php">http://www-usr.inf.ufsm.br/~sandro/elc139/tarefa1.php</a>

Os computadores SISD são as máquinas clássicas não paralelas da arquitetura de Von Neumann, com um único fluxo de instrução e um único fluxo de dados.

As SIMD funcionam com um único fluxo de instrução e múltiplos fluxos de dados. Correspondem ao caso das arquiteturas vetoriais em que a mesma operação é executada sobre múltiplos operandos e processadores.

Já as máquinas MIMD são o caso dos multiprocessadores, em que várias instruções podem ser executadas ao mesmo tempo em unidades de processamento diferentes, controladas por unidades de controle independentes (uma para cada unidade de processamento). Essa arquitetura permite execução de instruções diferentes para cada dado.

Por último, computadores MISD são os que executam diferentes instruções sobre a mesma posição da memória ao mesmo tempo. Essa arquitetura é impraticável pois não existem aplicações reais para ela.

Além da classificação de Flynn, também é possível encontrar na literatura uma classificação segundo o compartilhamento da memória. De acordo com De Rose e Navaux (2003), podemos afirmar que arquiteturas em que os processadores compartilham um único espaço de endereçamento de memória são chamadas de multiprocessadores. Por outro lado, arquiteturas que possuem replicação do conjunto processador/memória são chamadas de multicomputadores. Neste último caso, a comunicação entre os processos é efetuada por mensagens, através de uma rede de interconexão (HESS, 2003).

Atualmente, os multiprocessadores têm evoluído para um modelo genérico incluindo vários núcleos com CPU e memória, comunicando-se entre si através de uma rede de interconexão. Esse novo conceito de arquitetura foi chamado de *System-on-Chip* (SoC) por Culler, Singh e Gupta (1998).

#### 2.1.1 Sistemas em Chip

São arquiteturas compostas por um processador agregado a coprocessadores específicos para diversas finalidades, como processamento de imagens, sinais, gerenciamento de entrada e saída, etc.

A união das tecnologias SoC e multiprocessadores tornou possível a criação dos MPSoC (*MultiProcessor System-on-Chip*) (WOLF; JERRAYA; MARTIN, 2008). A tecnologia de MPSoCs não consiste apenas em inserir diversos processadores em um único chip. O conceito de MPSoC define que os processadores devem ser otimizados para a aplicação alvo, e blocos computacionais desnecessários à aplicação são removidos para economizar energia e área do circuito integrado (JERRAYA; WOLF, 2004).

#### 2.1.2 Redes em Chip

Com vários processadores interconectados, o desafio dos projetistas tornou-se evitar a perda de desempenho durante a troca de informação entre as unidades processantes (ou *Intelectual Property* – IP). A arquitetura de comunicação mais simples utilizada por MPSoCs é a de canais ponto a ponto (Figura 3a), em que cada IP está ligado a cada um dos outros IPs. No entanto, esse modelo torna-se inviável no contexto de escalabilidade. As arquiteturas de barramento (Figura 3b) são uma solução para o aumento da rede, pois interligam todos os IPs através de uma única ligação. Contudo, este tipo de conexão tende a causar atrasos no envio de mensagens devido à disputa pelo canal de transmissão.

Núcleo Núcleo Núcleo Núcleo Núcleo Núcleo Núcleo (b)

Figura 3 - Estruturas de Interconexão: (a) ponto-a-ponto; (b) barramento

Fonte: Araújo (2012)

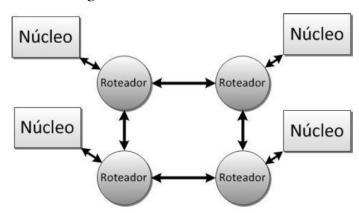

Uma proposta de comunicação entre os IPs são as Redes-em-Chip (*Network-on-Chip* – NoC) (BENINI; DE MICHELI, 2002). As NoCs fazem analogia a redes de computadores tradicionais. Elas podem ser definidas como uma estrutura de roteadores ligados ponto a ponto e conectados aos IPs da MPSoC, de modo a prover a comunicação entre eles. As informações ou mensagens são trocadas através de pacotes de dados. O uso de NoCs permite gerenciar a eficiência energética, comunicação e a escalabilidade do SoC (BENINI; DE MICHELI, 2002). A Figura 4 mostra a ligação entre núcleos por uma NoC.

O aumento da complexidade das SoCs trouxe problemas com relação ao consumo de energia, latência na sincronização, vazão de comunicação. Esses fatores motivaram o uso das NoCs para facilitar a separação entre comunicação e computação.

Figura 4 - Modelo de uma NoC

Fonte: Araújo (2012)

Os primeiros trabalhos sobre a ideia de NoCs datam de 1992 (TEWKSBURY; UPPULURI; HORNAK, 1992). Assim como nas redes de computadores, as NoCs podem ser caracterizadas por topologia, chaveamento, controle de fluxo, arbitragem, roteamento e memorização (ZEFERINO, 2003) (LEE et al, 2007).

Segundo Concer, Iamundo e Bononi (2009), as NoCs são definidas por um conjunto de três elementos: interfaces de rede, roteadores e enlaces (*links*). Esses componentes juntos são responsáveis por uma arquitetura de comunicação de chaveamento de pacotes, os quais encapsulam as mensagens ou as informações a serem transmitidas de um núcleo fonte até um destino através da infraestrutura

oferecida pela rede. O pacote é formado por um conjunto de palavras contendo um cabeçalho, que normalmente carrega informações do pacote, da aplicação e dos roteadores de origem e destino e a mensagem propriamente dita.

As NoCs podem ser configuradas para funcionarem com diferentes topologias, algoritmos de roteamento, chaveamento, controle de fluxo, memorização, etc. Tal característica torna fácil encontrar exemplos de implementações de NoCs na literatura. Um dos primeiros trabalhos sobre NoC foi a arquitetura SPIN (*Scalable Programmable Interconction Network*) de Adriahantenaina et al (2003), que utiliza uma topologia de árvore gorda (*fat tree*). Outra arquitetura bem citada é a SoCIN (*SoC Interconnection Network*) de Zeferino e Susin (2003). Outros exemplos são a HERMES (MORAES et al, 2004) e a STORM (REGO, 2006).

Para este trabalho, foi escolhida uma NoC descrita por Araújo (2012) intitulada de *Integrated Processing* NoC *System*, IPNoSys, que será descrita em detalhes na seção 2.4.

## 2.2 Pipeline

O pipeline foi adicionado aos computadores a partir do processador 486 da Intel, embora seu conceito inicial de divisão de instruções já tenha sido desenvolvido desde o processador 8086, o qual continha duas unidades distintas que processavam partes diferentes da instrução (VASCONCELOS, 2002). Esta ideia se baseia na criação de um semiparalelismo, dividindo a instrução em diferentes estágios que podem ser executados em paralelo, com o objetivo de aproveitar as unidades que ficariam ociosas em algum momento do processamento.

De forma geral, a técnica de *pipeline* não aumenta a velocidade de execução de uma instrução. O que ela faz é aumentar o início da execução das próximas instruções, de modo análogo a uma linha de produção. O termo "semiparalelismo" foi descrito por Patterson e Hennessy (2014) devido ao fato que duas (ou mais) instruções não são executadas em paralelo, mas que, em um determinado momento, elas estão simultaneamente em processo de execução.

Para ser compatível com pipeline, o processador deve ter as unidades funcionais do caminho de dados bem divididas, de modo que a saída de um estágio deve alimentar o estágio seguinte. Um dos projetos precussores do pipeline foi o MIPS (Microprocessor Without Interlocked Pipeline Stages) (PATTERSON; HENNESSY, 2014).

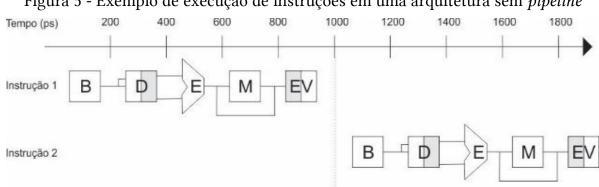

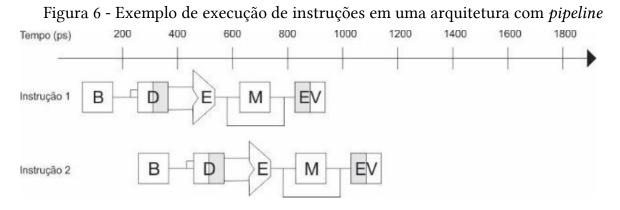

O trabalho de Nunes (2012) desenvolveu um processador baseado em MIPS contendo cinco estágios, sendo eles: Busca (identificado pela letra B), Decodificação (D), Execução (E), Acesso à Memória (M) e Escrita de Volta (EV). A Figura 5 mostra um exemplo de uma instrução sendo executada neste processador, mas sem utilização de pipeline.

Figura 5 - Exemplo de execução de instruções em uma arquitetura sem *pipeline*

Fonte: Nunes (2012)

Pode-se observar que a instrução 2 só começa o estágio de Busca quando a instrução 1 finaliza o estágio de Escrita de Volta. No mesmo processador utilizando pipeline, o estágio de Busca da instrução 2 pode ser iniciado assim que o estágio de Busca da instrução 1 tiver sido concluído. A Figura 6 exemplifica este cenário.

Fonte: Nunes (2012)

Assumindo condições ideais, o desempenho de um processador com *pipeline* será proporcional ao número de estágios que ele contém e pode ser calculado da seguinte forma:

$$Tempo \ do \ programa \ com \ pipeline = \frac{Tempo \ do \ programa \ sem \ pipeline}{N^{\underline{o}} \ de \ est\'agios \ do \ pipeline}$$

No entanto, há situações em que a instrução seguinte não pode ser iniciada antes do término da instrução anterior. Estas situações são denominadas de dependências e podem ser de três tipos:

- a) Dependências de Dados: acontece quando a próxima instrução necessita do valor do resultado da instrução anterior.

- b) Dependências de Controle: as instruções de desvio são as causadoras desse tipo de dependência. Quando as instruções são executadas com *pipeline*, ao surgir um desvio, as instruções seguintes, que já haviam entrado no *pipeline*, são descartadas. Isso causa uma perda de desempenho.

- c) Dependência Estrutural: acontece quando duas instruções no *pipeline* tentam acessar o mesmo recurso ao mesmo tempo.

As situações de dependências fazem com que o processador não consiga preencher os estágios do *pipeline*, resultando em perda do desempenho. Existem algumas técnicas para tratamento de dependências, mas a implementação desses mecanismos gera uma complexidade maior para a unidade de controle (PILLA; SANTOS; CAVALHEIRO, 2009). Contudo, a técnica de *pipeline* ainda é indiscutivelmente vantajosa no ganho de desempenho para processadores. Diversas famílias de processadores comerciais atuais, inclusive a Intel Core®, implementam o *pipeline* em suas arquiteturas (TORRES, 2013).

Quando as unidades funcionais do *pipeline* são replicadas, podemos ter instruções sendo executadas de forma paralela em todos os estágios. Para processadores desse tipo, damos o nome de superescalares (PATTERSON; HENNESSY, 2014). No entanto, é fácil notar que o ganho de desempenho dos processadores superescalares está ligado à quantidade de réplicas das unidades funcionais e às dependências das instruções. A Figura 7 contém o modelo de um processador

superescalar com suas unidades funcionais duplicadas. As regras de *pipeline* nessa arquitetura são as mesmas. Pode-se observar que apenas nessa arquitetura é que, de fato, as instruções são executadas em paralelo.

Fonte: Autoria própria

Máquinas superescalares têm seu paralelismo em nível de instrução (duas ou mais instruções são executadas ao mesmo tempo). Desta forma, elas são classificadas como arquiteturas paralelas ILP (*Instruction Level Paralelism*). Além do ILP, é possível encontrar arquiteturas com paralelismo em nível de thread (*Thread-Level Paralellism* – TLP) explorado por arquiteturas multicores e em nível de dados (*Data-Level Paralelism* – DLP) utilizado em processadores vetoriais (SANKARALINGAM et al, 2003).

#### 2.3 Software Pipelining

A técnica de software *pipelining*, descrita por Lam (1988), afirma que computadores com arquiteturas do tipo VLIW (*Very Long Instruction Word*) possuem componentes funcionais que possibilitam que instruções dentro de um laço de

repetições possam ser executados de forma simultânea, similar ao *pipeline*. De acordo com Jones e Allan (1990), o conceito de software *pipelining* é descrito como conseguir iniciar a segunda iteração de um laço de repetição antes que a primeira iteração tenha finalizado. Para efeito didático, tomemos o algoritmo descrito pela Figura 8 para ilustrar o conceito do software *pipelining*.

Figura 8 - Exemplo de Laço de Repetição

```

1   algoritmo exemplo 1

2     x, i, op1, op2, op3 : inteiro

3     para i de 0 ate x faca

4     | op1 = i

5     | op2 = op1 + 1

6     | op3 = op2 + 2

7     fimpara

8   fimalgoritmo

```

Fonte: Autoria Própria

Em arquiteturas convencionais, cada instrução do algoritmo da Figura 8 seria executada de forma sequencial, uma após a outra. Na Seção 2.2, foi possível verificar que, utilizando o *pipeline*, pode-se iniciar a instrução seguinte antes de finalizar a instrução anterior, por meio do *pipeline* convencional.

No entanto, para o exemplo descrito, o *pipeline* convencional não pode ser empregado, pois há uma dependência de dados entre as instruções. A instrução na linha 6 depende do resultado da instrução da linha 5, que depende da instrução da linha 4. Com isso, a unidade funcional de decodificação não pode ler os dados na memória antes deles serem escritos como resultado da instrução anterior. Devido aos problemas de dependências e considerando o valor de iterações x = 5, o algoritmo será executado como mostra a Figura 9.

Figura 9 - Execução Sequencial do Algoritmo Exemplo

Iterações do Laço 1 4 2 5 3 1 op1=i 2 op2=op1+1 3 op3=op2+2 4 op1=i 5 op2=op1+1 6 op3=op2+2 7 op1=i 8 op2=op1+1 9 op3=op2+2 10 op1=i 11 op2=op1+1 12 op3=op2+2 13 op1=i 14 op2=op1+1 15 op3=op2+2

Fonte: Autoria Própria

Através do software *pipelining*, as instruções dentro do laço serão reorganizadas entre suas unidades funcionais, de modo que possam ser executadas de forma semelhante a um *pipeline* (JONES; ALLAN, 1990), como mostrado pela Figura 10.

Figura 10 - Execução do Algoritmo com Software pipelining (Ciclos/Iteração)

|        | Iterações do Laço |           |           |           |           |           |  |

|--------|-------------------|-----------|-----------|-----------|-----------|-----------|--|

|        |                   | 1         | 2         | 3         | 4         | 5         |  |

| Ciclos | 1                 | op1=i     |           |           |           |           |  |

|        | 2                 | op2=op1+1 | op1=i     |           |           |           |  |

|        | 3                 | op3=op2+2 | op2=op1+1 | op1=i     |           |           |  |

|        | 4                 |           | op3=op2+2 | op2=op1+1 | op1=i     |           |  |

|        | 5                 |           |           | op3=op2+2 | op2=op1+1 | op1=i     |  |

|        | 6                 |           |           |           | op3=op2+2 | op2=op1+1 |  |

|        | 7                 |           |           |           |           | op3=op2+2 |  |

Fonte: Autoria Própria

Existem várias formas de implementação de software *pipelining*, incluindo até modelos heurísticos para reorganização das instruções pelo compilador (RAU, 1994). Contudo, diversos autores mostram que a implementação da técnica de software *pipelining* garante um ganho de desempenho em aplicações que envolvem laços de repetição, tais como Jones e Allan (1990), Rau (1994), Goldberg et al (2002), Thies,

Chandrasekhar e Amarasinghe (2007) e Wang et al (2010). Adicionalmente, Govindarajan, Altman e Gao (1996) dizem que o esforço de implementar a técnica de software *pipelining* vale a pena devido à sua simplicidade de descrição na arquitetura, se comparada ao ganho de desempenho proporcionado.

#### 2.4 IPNoSys

Neste trabalho foi utilizada a rede em chip IPNoSys, que foi modificada para implementação da técnica de software *pipelining*. Os detalhes relevantes desta arquitetura em seu formato original são apresentados nesta seção.

#### 2.4.1 Visão Geral

A *Integrated Processing NoC System*, ou IPNoSys (Figura 11), é uma arquitetura proposta por Araújo (2012), baseada em NoC.

Fonte: Araújo (2012)

A principal diferença entre IPNoSys e outras NoCs é a alteração dos roteadores a fim de prover, além da transmissão de pacotes, o processamento de dados. Isso é possível inserindo-se uma unidade lógica e aritmética (ULA) e uma unidade de sincronização (*sinchronization unit* - SU) no roteador. Essa estrutura modificada foi descrita em Araújo et al (2009) e chamada de Unidade de Processamento e Roteamento ou RPU (*Routing and Processing Unit*).

De modo geral, a IPNoSys é uma rede de RPUs com topologia grelha-2D de dimensão quadrada, ou seja, o número de linhas é igual ao de colunas. A ordem da rede (número de linhas e colunas) pode ser configurada de acordo com a aplicação. Cada RPU é ligada à sua vizinha através de um barramento.

Nos quatro cantos da rede existem, ligadas a cada RPU adjacente, uma Unidade de Acesso à Memória – MAU (*Memory Access Unit*). Uma das MAUs é diferenciada para prover o gerenciamento de entrada e saída (E/S). Ela é ligada ao IONode, que faz a ponte com os dispositivos de E/S. No modelo IPNoSys, o processamento ocorre quando uma MAU injeta pacotes na rede. Ao chegar na RPU, as instruções vão sendo processadas e roteadas para o próximo destino.

A relação das MAUs com as RPUs torna possível que todas injetem pacotes simultaneamente na rede, permitindo a execução paralela de aplicações. Os pacotes no IPNoSys utilizam o modelo *backpacker* (TIEG, 2010), em que os dados estão sempre presentes junto com as instruções, em analogia aos mochileiros, que carregam tudo que o que lhes é essencial. Com isso, é possível reduzir a quantidade de acessos à memória. Mais detalhes sobre os pacotes do IPNoSys serão abordados na Seção 2.4.3. O modelo de programação da IPNoSys se classifica como "tudo explícito", sendo responsabilidade do programador fazer toda a configuração para execução dos pacotes (SKILLICORN; TALIA, 1998).

Os pacotes do IPNoSys são sequências de instruções e dados que contém a aplicação a ser executada. Os pacotes são inseridos na rede pelas MAUs e são transferidos para as RPUs através de um algoritmo de roteamento. Cada RPU no caminho do pacote retira pelo menos uma instrução, a executa, insere os resultados no

pacote (se houver) e o roteia para a próxima RPU. A cada RPU que o pacote passa, vai diminuindo até ser consumido por completo.

Para efeito de simulação, a arquitetura foi totalmente descrita utilizando SystemC (ARAÚJO, 2012). O SystemC é uma extensão da linguagem C++ que possibilita a simulação de sinais e processos de hardware, semelhante às linguagens de descrição de hardware (BLACK et al, 2005).

#### 2.4.2 Unidade de Roteamento e Processamento

A RPU é o elemento responsável pelo roteamento dos pacotes e execução de instruções. Sua estrutura é composta por uma Unidade Lógica e Aritmética, responsável por executar as instruções descritas nos pacotes das aplicações, uma Unidade de Sincronismo (SU – *Synchronization Unit*), *buffers*, *crossbar* e árbitros (um associado a cada porta), como detalhado na Figura 12.

Figura 12 - Unidade de Processamento e Roteamento

Fonte: Araújo (2012)

Ao chegar na RPU, o pacote é armazenado em um *buffer* na entrada. As RPUs mais internas à rede têm quatro entradas, enquanto as mais externas possuem apenas três. Cada entrada possui pelo menos dois buffers, um para cada canal virtual. Depois de armazenado, o árbitro correspondente analisa o conteúdo do pacote a fim de verificar o seu tipo. Caso seja um pacote regular, a instrução e os operandos são retirados do pacote e enviados para a ULA. Caso seja um pacote de outro tipo, o *crossbar* se responsabiliza de chavear para uma das portas de saída. Se o *buffer* de entrada da próxima RPU estiver cheio, inicia-se um processo chamado de execução localizada. Como a RPU não pode transmitir, ela mesma se encarrega de executar as próximas instruções até que consiga transmitir.

Pode-se dizer que o árbitro é o elemento principal de controle da RPU. Ele é responsável por identificar a instrução, enviá-la para ULA, SU ou MAU. Após a execução de uma instrução, o árbitro passa apenas a transmitir o pacote, sempre verificando se é o momento de inserir algum resultado gerado pela instrução que executou. Ele faz isso verificando se a posição de inserção do resultado coincide com o contador de palavras transmitidas. Os árbitros ficam localizados nas portas de saídas e controlam as disputas pelos canais virtuais (das saídas) utilizando o algoritmo *round-robin*, como em um roteador tradicional.

#### 2.4.3 Formato do Pacote

O Pacote no IPNoSys é formado por palavras de 32 bits, com quatro bits extras (bits de controle) usados para identificar o tipo da palavra (Figura 13). As três primeiras palavras de um pacote são compostas por seu cabeçalho. As palavras seguintes são as instruções e operandos da aplicação. Por fim, a última palavra do pacote contém a identificação de fim do pacote. O cabeçalho e o fim de pacote sempre contém três e uma palavra, respectivamente, enquanto que as de instruções e operandos podem variar dependendo da aplicação.

Figura 13 - Formato do pacote IPNoSys

Fonte: Araújo (2012)

No IPNoSys são encontrados quatro tipos de pacotes. Os Regular são os que carregam as instruções e operandos para serem executados nas RPUs. Além dele, existem os pacotes de controle, que são pacotes endereçados às MAUs a fim de efetuar alguma operação de leitura e escrita na memória ou sincronização; o pacote *Caller*, que faz uma operação similar a uma chamada de função; e o pacote Interrompido, que informa que a RPU está aguardando algum evento (como a entrada/saída) ou houve algum problema na execução do pacote regular que estava sendo processado. Os pacotes regulares da aplicação são gerados pelo compilador. Os outros tipos são gerados automaticamente pela arquitetura em tempo de execução da aplicação.

Em cada palavra do pacote, apenas um bit de controle pode estar ativo. Esses bits são identificados pelas letras "C" (cabeçalho), "F" (fim de pacote), "I" (instrução) e "O" (operandos), na Figura 13. Nas três palavras de cabeçalho são encontrados campos relativos a origem e destino do pacote, quantidade de instruções e outros detalhes do programa. Para este trabalho, as palavras de cabeçalho e fim de pacote foram ignoradas, sendo necessário apenas um aprofundamento dos campos das palavras de instrução e operandos. A palavra de instrução é definida por quatro campos (além dos bits de controle):

- a) ID da Instrução (8 bits): Identifica a instrução a ser executada.

- b) NO (2 bits): Número de operandos utilizados para executar a instrução.

- c) Resultado\_1 (11 bits): em pacotes de controle, este campo é utilizado para indicar o endereço da MAU que deverá executar a instrução à qual está associado. Nos demais pacotes, ele é utilizado para indicar a posição em que o resultado da operação deve ser inserido no mesmo pacote.

- d) Resultado\_2 (11 bits): este campo pode indicar a quantidade de operandos, menos um, envolvidos na instrução (se o campo NO contiver o valor "11<sub>b</sub>"); ou uma segunda posição no pacote em que o resultado da instrução também deve ser inserido.

Nas palavras de operandos, os 32 bits são utilizados como operandos da instrução. Nas palavras de instrução, apenas o bit de controle "I" deve estar ativado, enquanto que nas palavras de operando, apenas o bit "O".

#### 2.4.4 Roteamento

Na arquitetura IPNoSys, a RPU retira uma instrução do pacote e transfere o resto do pacote para a próxima RPU. Portanto, deve haver um caminho longo suficiente na rede para que o pacote possa caminhar entre as RPUs até ele ser consumido por completo. O algoritmo de roteamento utilizado para prover esse recurso foi denomidado de *Spiral Complement* e apresentado em Araújo et al (2009). O *Spiral Complement* define uma série de caminhos em espirais. A Figura 14 mostra os caminhos percorridos por um pacote que é injetado por cada uma das MAUs.

Figura 14 - Roteamento Spiral Complement

Fonte: Araújo (2012)

O modelo em espirais contribui para que o pacote percorra o máximo de caminhos possíveis. Entretanto, pacotes com um número alto de instruções podem chegar até o fim do caminho e ainda haver instruções para serem executadas. Nesses casos, ao chegar no fim do percurso, o pacote pode entrar numa situação de *deadlock*, em que ainda há instruções para serem executadas mas não existe RPU disponível para execução. Nesses casos, a fim de evitar o *deadlock*, a RPU entra em modo de execução localizada. Na execução localizada, a RPU para de transmitir pacotes e começa a executar o resto das instruções no pacote até que possa começar a transmitir novamente ou até que o pacote chegue ao fim.

O algoritmo *Spiral Complemet* é usado para rotear apenas os pacotes regulares. Os outros tipos de pacote, que têm como função apenas comunicação, são roteados pelo algoritmo de roteamento XY. Nesse algoritmo, o caminho do pacote é dividido em

duas partes. Aos sair da origem, o pacote caminha horizontalmente (eixo X) até a coluna onde se encontra o seu destino. A partir daí, o pacote percorre a rede no sentindo vertical (eixo Y) até chegar em seu objetivo (Figura 15).

Primeiro no sentido 0,0 0,1 0,2 0,3 1,2 1,0 1,1 1,3 **LEGENDA** Origem Destino 2,0 2,1 2,2 2,3 Depois no sentido 3,0 3,1 3,2 3,3

Figura 15 - Roteamento XY

Fonte: Araújo (2012)

Outros algoritmos de roteamento foram desenvolvidos para IPNoSys a fim de tentar maximizar a quantidade de saltos antes de entrar em execução localizada. Os trabalhos de Cruz (2013) e Filho et al (2014), por exemplo, fizeram estudos de caso comparando o *Spiral Complement* com outros algoritmos de roteamento. Entretanto, tais algoritmos não serão abordados neste trabalho.

### 2.4.5 Programabilidade

Para se executar aplicações no sistema IPNoSys, é necessário descrever o programa através da Linguagem de Descrição de Pacotes (PDL – *Package Description Language*). A ISA (*Instruction Set Architecture*, ou conjunto de instruções) define 32 instruções, que são detalhadas na Tabela 1, divididas em 4 instruções aritméticas, 4 lógicas, 2 de deslocamentos, 4 de sincronização, 3 de acesso a memória, 6 de desvios condicionais, 1 incondicional, 2 auxiliares, 2 de E/S, 2 de sistema e 2 de chamada de procedimento.

Tabela 1 - Conjunto de Instrução da IPNoSys

| CodOp     | Instrução | Tipo             | Operandos | Descrição                                          |  |  |

|-----------|-----------|------------------|-----------|----------------------------------------------------|--|--|

| 0         | ADD       | Aritmética       | 2         | Soma 2 inteiros                                    |  |  |

| 1         | SUB       | Aritmética       | 2         | Subtrai 2 inteiros                                 |  |  |

| 2         | MUL       | Aritmética       | 2         | Multiplica 2 inteiros                              |  |  |

| 3         | DIV       | Aritmética       | 2         | Divide 2 inteiros                                  |  |  |

| 4         | NOT       | Lógica           | 1         | Negação de 1 valor                                 |  |  |

| 5         | AND       | Lógica           | 2         | Conjunção de 2 valores                             |  |  |

| 6         | OR        | Lógica           | 2         | Disjunção de 2 valores                             |  |  |

| 7         | XOR       | Lógica           | 2         | Ou-exclusivo de 2 valores                          |  |  |

| 8         | RSHIFT    | Deslocamento     | 2         | Desloca <i>n</i> bits de um valor à direita        |  |  |

| 9         | LSHIFT    | Deslocamento     | 2         | Desloca $n$ bits de um valor à esquerda            |  |  |

| 10        | LOAD      | Acesso à Memória | 1         | Solicita um valor da memória                       |  |  |

| 11        | STORE     | Acesso à Memória | Vários    | Armazena um valor na memória                       |  |  |

| 12        | EXEC      | Sincronização    | 1         | Ordena a injeção de um pacote                      |  |  |

| 13        | SYNEXEC   | Sincronização    | Vários    | Ordena a injeção de um pacote após sincronização   |  |  |

| 14        | SYNC      | Sincronização    | 1         | Sinal de sincronização para um pacote              |  |  |

| 15        | RELOAD    | Acesso à Memória | 1         | Retorna um valor carregado da memória              |  |  |

| 16        | BE        | Condicional      | 2         | Desvia se igual                                    |  |  |

| <i>17</i> | BNE       | Condicional      | 2         | Desvia se diferente                                |  |  |

| 18        | BL        | Condicional      | 2         | Desvia se menor                                    |  |  |

| 19        | BG        | Condicional      | 2         | Desvia se maior                                    |  |  |

| 20        | BLE       | Condicional      | 2         | Desvia se menor ou igual                           |  |  |

| 21        | BGE       | Condicional      | 2         | Desvia se maior ou igual                           |  |  |

| 22        | JUMP      | Incondicional    | 0         | Desvia incondicionalmente                          |  |  |

| 23        | COPY      | Auxiliar         | 1         | Copia 1 valor para outra instrução no mesmo pacote |  |  |

| 24        | NOP       | Auxiliar         | 0         | Sem operação                                       |  |  |

| 25        | SEND      | Sincronização    | 2         | Envia um valor para um ser inserido em um pacote.  |  |  |

| 26        | IN        | Entrada/Saída    | 3         | Recebe bytes do controlador de E/S                 |  |  |

| 27        | OUT       | Entrada/Saída    | 3         | Envia bytes ao controlador de E/S                  |  |  |

| 28        | WAKEUP    | Sistema          | 1         | Ordena a reinjetar um pacote antes interrompido    |  |  |

| 29        | NOTIFY    | Sistema          | 1         | Notifica estado de um pacote                       |  |  |

| 30        | CALL      | Procedimento     | Vários    | Faz a chamada de uma função/pacote                 |  |  |

| 31        | RETURN    | Procedimento     | 2         | Retorna o resultado de uma função para o chamador  |  |  |

Fonte: Araújo (2012)

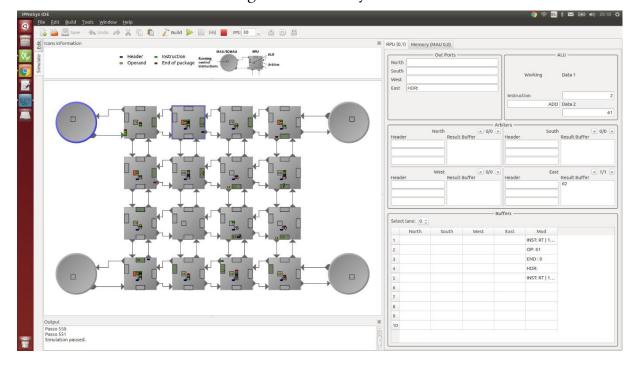

Utilizando este conjunto de instruções, é possível desenvolver aplicações que podem estar dispostas em um ou mais pacotes, cada um contendo instruções e operandos. A PDL é uma linguagem equivalente ao *assembly* e de modo análogo deve ser montada, traduzida e carregada na memória para que seja executada. Para simulação de programas na arquitetura, é utilizado um ambiente de programação e simulação descritos em SystemC (Figura 16). O próprio ambiente implementa um montador que traduz o programa descrito em PDL para o código objeto da arquitetura.

Figura 16 - Ambiente de Programação e Simulação IPNoSys

Fonte: Araújo (2012)

O programa em PDL deve ser escrito em um editor de texto qualquer. O montador converte o código em PDL no código objeto que é passado como parâmetro para o simulador, o qual inicializa as memórias e prossegue a execução da aplicação. Durante a simulação, vários dados estatísticos são produzidos e armazenados em um arquivo texto.

Segundo Araújo (2012), a IPNoSys também pode ser comparada às arquiteturas VLIW. Computadores VLIW possuem núcleos que executam um grupo de instruções em paralelo. As instruções são unidas em uma única palavra. O compilador é responsável por juntar as instruções e garantir que não haja dependências entre elas.

Mais detalhes sobre o IPNoSys podem ser encontrados consultando Araújo (2012), Araújo et al (2009) e Filho et al (2014).

#### 2.5 Trabalhos Relacionados

Como visto na Seção 2.3, a técnica de software *pipelining* traz um ganho sugestivo a muitas arquiteturas que a implementam para certas aplicações. Com isso, não é difícil encontrar autores que tenham trabalhado o tema.

Em 2007, Douillet e Gao (2007) implementaram a técnica de software pipelining em uma arquitetura multicore. O método utilizado consistia em separar as instruções livres de dependências em threads que eram entregues aos núcleos disponíveis para processamento. Quando uma instrução com dependência era encontrada, um sinal de wait era ativado e a aplicação era executada de forma sequencial, mesmo se houvesse núcleos disponíveis. Os resultados mostraram que a implementação teve um resultado favorável mesmo em aplicações com muitas dependências.

No trabalho desenvolvido por Gao et al (2009), foi desenvolvida uma técnica para explorar software *pipelining* em arquiteturas reconfiguráveis. O algoritmo foi implementado na linguagem C e convertido por meio de um software específico para simulação e testes na ferramenta ModelSim® da Altera©. Os resultados provaram que as arquiteturas com software *pipelining* tiveram um desempenho em torno de 35% melhor em comparação com os modelos originais.

Em Wei et al (2012), foi desenvolvido um método de software *pipelining* para arquiteturas com recursos limitados. O algoritmo proposto escalona instruções nos processadores a fim de reduzir a taxa de comunicação e acesso a memória. Esta nova técnica foi comparada com outros modelos de ILP e obteve um resultado similar no desempenho e melhor na eficiência no uso de memórias e comunicação.

## 2.5.1 Software *Pipelining* e IPNoSys

Mais recentemente, os trabalhos de Medeiros (2014) e Medeiros (2015) apresentaram uma técnica de software *pipelining* para a arquitetura IPNoSys. Para efeito de validação da técnica, foi desenvolvido um simulador em C++ para a IPNoSys.

O modelo proposto modificava a estrutura do pacote e o algoritmo de roteamento para criar o efeito desejado. As modificações feitas nos pacotes foram a substituição do campo *Apontador* no cabeçalho do pacote pelo campo *Nº de Iteração* e a inclusão de uma nova palavra entre cada instrução e seu operando. Essa nova palavra contém os campos *Contador da Instrução* e *Nº de Iteração*. A Figura 17 mostra o novo pacote criado.

Destino Destino Origem Origem Nºde Re-C Instruções Rotear ID do Programa ID do Pacote C --- 16 ---Nº de Instrução Endereço da Mau 0 Nº de Iteração por RPU 16 0 ID da Instrução F Result 1 Result 2 Contador da Instrução 0 Nº de Iteração C Valor do Operando 0 Terminador 0 Nº de Iteração

Figura 17 - Formato de Pacote Modificado Para Software *Pipelining*Bits de Controle

Fonte: Medeiros (2014)

O modelo de execução proposto funciona da seguinte forma: A RPU retira uma instrução do pacote e verifica a próxima palavra. Se for um operando, a instrução é executada normalmente. Mas se for uma palavra com o as instruções de laço, a RPU executa a operação e envia a instrução e seus operandos para a próxima RPU para que a mesma seja executada novamente.

Os testes foram feitos a partir de uma aplicação genérica com um laço de repetição. As quantidades de iterações e tamanho da rede foram modificadas a fim de

se ter um quadro geral de várias situações possíveis. Os resultados mostraram que todas as simulações com software *pipelining* obtiveram um desempenho melhor do que a implementação com laço tradicional.

Apesar dessa proposta ter se mostrado bem melhor na execução de laços do que no modelo da IPNoSys original, o modelo proposto por Medeiros (2014) apresenta algumas fragilidades. O fato de se incluir uma nova palavra a cada instrução do laço e executar transmissões de pacotes em cada iteração são fatores negativos a esse modelo pois, segundo Araújo (2012), transmitir pacotes é o principal fator de queda de desempenho da IPNoSys. Outro ponto negativo é a limitação na quantidade de repetições possíveis para cada instrução. Como a instrução executa novamente a cada RPU que passa, a quantidade de execuções fica limitada a quantidade de RPUs no caminho do pacote. Como solução, o autor utilizou um algoritmo de roteamento implementado por Cruz (2013). Esse novo roteamento cria um caminho em ziguezague de que o pacote possa sair de uma RPU, percorrer toda a rede e voltar a RPU original. Essa rota gera uma espécie de caminho "infinito" que o pacote pode percorrer e ter suas instruções executadas repetidamente.

Vale ressaltar também que a comparação dos resultados apresentados por Medeiros (2014) com a arquitetura original é prejudicada, visto que os testes não foram executados no mesmo simulador SystemC desenvolvido por Araújo (2012), e sim em um simulador próprio em linguagem de alto nível.

Diferentemente de Medeiros (2014) e Medeiros (2015), o trabalho apresentado nesta dissertação modificou a arquitetura da IPNoSys (montador e simulador originais) para que esta possa reconhecer e executar a técnica de software *pipelining* em aplicações reais, sem a alteração da estrutura do pacote ou algoritmo de roteamento e tentando reduzir a quantidade de transmissão entre as RPUs. A nova arquitetura apresentada tem compatibilidade completa com os programas desenvolvidos para a IPNoSys original e possivelmente, com desempenho melhorado nos laços de repetição, assim como aponta Medeiros (2014).

### 3 SOFTWARE PIPELINING NA IPNOSYS

O modelo de execução original da IPNoSys executa laços de repetição reinjetando o mesmo pacote na rede repetidamente. Esse processo se dá pela utilização das instruções EXEC e SEND ao fim do pacote. A instrução EXEC é responsável por fazer uma chamada a uma determinada MAU para injetar um novo pacote na rede, que no caso de laço de repetição, é o mesmo pacote que acabou de ser finalizado. A instrução SEND por sua vez, serve para enviar resultados entre pacote. A cada iteração do laço, instruções SENDs enviam os resultados para o novo pacote e a instrução EXEC chama o pacote para rede. Esse procedimento se repete conforme a quantidade de vezes definida pelo laço de repetição. Tal operação, apesar de funcional, tem o desempenho prejudicado pela quantidade de mensagens trocadas entre as RPUs e a MAU, para leitura e gravação de valores na memória e requisições para reinjetar o pacote.

É importante ressaltar que o laço deve ser composto por três pacotes. O primeiro com o código antes do laço de repetição que deve chamar o segundo pacote. O segundo pacote é o laço propriamente dito. No final deste, há uma tomada de decisão para determinar se o laço chegou ao fim ou se deve ser repetido novamente. Se houver uma nova iteração, o valor da variável de controle é incrementado e o pacote é novamente injetado na rede. Caso o laço tenha sido concluído, é chamado o terceiro pacote que representa o código após o laço. Na Figura 18 é mostrado esse procedimento. As instruções EXEC e SEND na Figura 18 representam pacotes de controle que são enviados das RPUs até a MAU que a executará tantas vezes quanto for a lógica do laço de repetição.

Pacote 2

Laço

Pacote 0

Finalizador

EXEC

enquanto

i < x

Figura 18 - Laço de Repetição Tradicional no IPNoSys

De acordo com o apresentado na Seção 2.3, é possível utilizar a técnica de software *pipelining* para se conseguir um ganho de desempenho. Como forma de contribuir para o projeto IPNoSys, este trabalho implementou da técnica de software *pipelining* para a arquitetura em questão, com a avaliação do ganho de desempenho adquirido. A nova versão do IPNoSys software *pipelining* é dotada de mecanismos que executam instruções dentro de um laço de repetição de forma paralela, extraindo o máximo de desempenho do ILP.

#### 3.1 Visão Geral

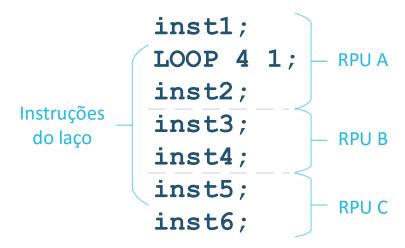

Para a implementação da técnica de software *pipelining*, criou-se duas novas instruções para a ISA da IPNoSys, chamadas de LOOP e RT (Tabela 2). A instrução LOOP serve para configurar as RPUs, delimitando quantas instruções pertencem ao laço e informando a quantidade de repetições as RPUs devem executar tais instruções. E a instrução RT transmite dados entre as RPUs quando há dependência de dados entre as instruções.

Tabela 2 - Instruções LOOP e RT

| CodOp | Instrução | Tipo              | Operandos | Descrição                                                        |

|-------|-----------|-------------------|-----------|------------------------------------------------------------------|

| 32    | LOOP      | Controle de Fluxo | 1         | Define a operação de loop utilizando software <i>pipelining</i>  |

| 33    | RT        | Auxiliar          | 1         | Carrega dados entre as instruções dentro de um laço de repetição |

Fonte: Autoria Própria

## 3.1.1 Instrução LOOP

A instrução LOOP utiliza dois parâmetros para configurar as RPUs. No espaço destinado ao *Resultado 1*, deve ser informada quantas das próximas instruções fazem parte do laço de repetição. Já no espaço dedicado ao Resultado 2, quantas instruções cada RPU no caminho do pacote vai executar (detalhamento na seção 3.2.1). A única palavra de operando, contém a quantidade de repetições que o laço deve executar. A Figura 19 contém a visão do programador (a) e os campos da palavra da instrução LOOP (b).

Número de instruções do laço e IPR LOOP 1 LOOP qi ipr; 2 qr; Número de repetições (a) Quantidade de Número de instruções CodOp da instruções dentro do laco de Instrução LOOP executadas por RPU repetição Instrução 0  $\leftarrow 1 \rightarrow \leftarrow 1 \rightarrow \leftarrow 1 \rightarrow \leftarrow 1 \rightarrow \leftarrow$ 11 -11 Operando 0  $\leftarrow$ 1 $\rightarrow$  $\leftarrow$ 1 $\rightarrow$  $\leftarrow$ 1 $\rightarrow$  $\leftarrow$ 1 $\rightarrow$  $\leftarrow$ 1 32 Número de repetições

Figura 19 - PDL da Instrução LOOP (a) e formato da palavra (b)

Fonte: Autoria Própria

(b)

Essa estratégia de informar a quantidade de instruções que fazem parte do laço serve para delimitar as instruções dentro dele. A Figura 20 mostra um algoritmo genérico com a sintaxe da instrução LOOP em PDL. Nela, de acordo com os parâmetros de LOOP, as instruções "inst2" e "inst3" seriam executadas dez vezes.

Figura 20 - LOOP Exemplo 01

```

1

inst1

LOOP 2 1;

// Quantidade de instruções do laço e IPR

2

3

// Quantidade de repetições

10;

4

inst2

// Inst. executada 10 vezes pela RPU A

// Inst. executada 10 vezes pela RPU B

5

inst3

6

Inst. Fora do laço de repetição

inst4

```

Enquanto o valor definido no campo *Resultado\_1* diz a quantidade de instruções que fazem parte do laço, o valor do campo *Resultado\_2* define a quantidade de instruções que serão executadas por cada RPU. Se esse valor for omitido pelo programador, o compilador define esse valor como "1" por padrão. Mais detalhes da utilidade desse campo serão mostrados nas sessões seguintes.

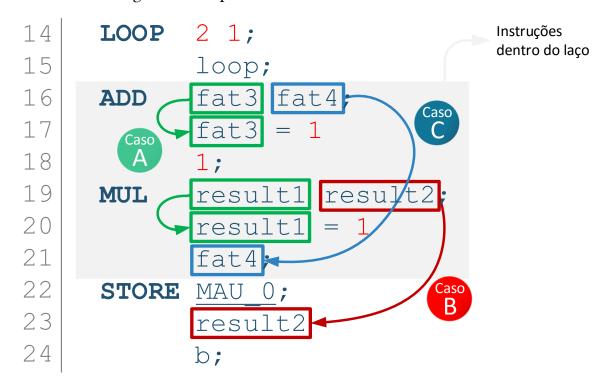

## 3.1.2 Instrução RT

O acrônimo RT foi usado para simbolizar o termo "retransmitir". A função dessa instrução é enviar o resultado de uma operação dentro do laço quando há dependência de dados com outras instruções que também estão dentro do laço. Observando o algoritmo da Figura 21, podemos perceber que a variável op2 depende de op1 e a variável op3, depende de op2. Em um cenário de execução com software pipelining proposto por este trabalho, as instruções das linhas 4, 5 e 6 ficariam em unidades funcionais diferentes. De modo que a unidade que estivesse executando a instrução da linha 4, deve enviar o resultado da operação para a unidade que esteja executando a linha 5 e assim por diante.

Figura 21 - Exemplo de Laço de Repetição Com Dependência de Dados

Fonte: Autoria própria

A instrução RT é utilizada para encaminhar o resultado da operação de uma RPU para outra quando se está dentro de um laço de repetição. O formato da instrução RT é mostrado na Figura 22. Assim como as instruções RETURN, RELOAD, NOTIFY etc, a instrução RT não está disponível para o programador. O árbitro que está executando o pacote é que cria a instrução em tempo de execução de forma transparente para o usuário.

Os campos da palavra da instrução RT são diferenciados em relação as outras instruções da IPNoSys. O fato se deve a quantidade de informações que a RPU necessita para que um dado seja salvo em um de seus *buffers* de resultado. Deste modo, o pacote contendo a instrução RT deve transportar as informações do endereço da RPU e a porta do destino que irá receber o dado, a porta e o canal virtual de origem, o endereço da palavra e o dado propriamente dito. Para isso, o árbitro que está executando a instrução que irá propagar o resultado identifica a RPU destino e envia para a Unidade de Sincronização (SU) duas palavras como mostra o diagrama da Figura 22.

Canal virtual da origem

Porta da origem

RPU

destino

RPU

AD

ADDR

C F I O

RT

LAN

AO

RPU

AD

ADDR

C F I O

Operando

Resultado

Figura 22 - Palavras da Instrução RT do árbitro para SU

Fonte: Autoria própria

Ao chegar na SU, as duas palavras são adicionadas a uma palavra de cabeçalho e uma palavra de fim de pacote para criar um pacote de controle (Figura 23). A união destas 4 palavras forma um pacote de controle que é injetado na rede e roteado até a

RPU que estará executando a operação que necessitará do dado. As informações para roteamento são retiradas da palavra do RT e colocadas no cabeçalho. Depois do pacote pronto, a palavra RT fica semelhante as palavras das demais instruções da IPNoSys.

Canal virtual da origem Porta da origem **RPU RPU** Porta destino Origem destino 0 Destino Origem # Instruções LO AO  $\leftarrow$ 1 $\rightarrow$  $\leftarrow$ 1 $\rightarrow$  $\leftarrow$ 1 $\rightarrow$  $\leftarrow$ 1 $\rightarrow$ Re-rotear NO **ADDR**  $\leftarrow$ 1 $\rightarrow$  $\leftarrow$ 1 $\rightarrow$  $\leftarrow$ 1 $\rightarrow$  $\leftarrow$ 1 $\rightarrow$  $\leftarrow$ 1 8 11 0 ←1→←1→←1→←1→ Fim de Pacote ←1→←1→←1→

Figura 23 - Pacote de Controle com a Função RT

Fonte: Autoria própria

O campo "re-rotear" do cabeçalho não é utilizado nos pacotes de controle e foi convenientemente aproveitado para acondicionar as informações dos canais virtuais e portas. A palavra de instrução RT foi colocada no formato padrão das outras palavras da IPNoSys para evitar modificações no momento da decodificação quando ela chega na RPU destino.

É importante chamar atenção para o campo destinado ao endereço da palavra do dado (ADDR), que no momento em que o árbitro envia a instrução RT para a SU (Figura 22), é colocado em um campo com 10 bits. E no momento em que o pacote é criado pela SU, o ADDR volta a ter os 11 bits que as palavras de IPNoSys tem. Essa "compressão" da informação em 10 bits não gera problemas pois segundo Araújo

(2012), um pacote regular da IPNoSys pode conter até 256 instruções. Apenas as instruções STORE e SYNEXEC utilizam mais do que dois operandos. Com isso, num caso extremo onde todas as instruções da IPNoSys têm 4 palavras (uma de instrução e três operandos), o pacote teria 256 instruções + (3 \* 256 operandos). Ou seja, um total de 1.024 palavras de instruções onde poderiam ser inseridos resultados. Deste modo, são necessários apenas 10 bits ( $2^{10} = 1.024$ ) no campo  $Result_1 = Result_2$  para identificar todos os endereços possíveis em um pacote.

# 3.2 Implementação

A implementação do software *pipelining* na IPNoSys foi dividida em duas partes. A primeira foi a criação de mecanismos para a execução de instruções repetidas vezes, como em um laço de repetição. A segunda parte foi a identificação e tratamento das dependências de dados.

## 3.2.1 Definindo o Laço de Repetição

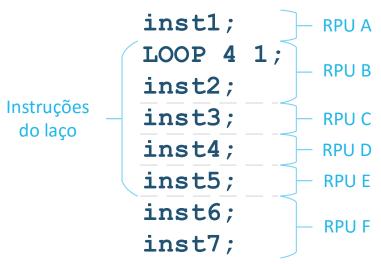

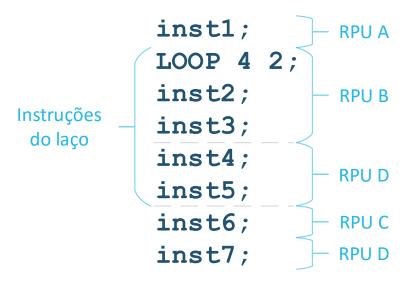

Para reconhecer e executar um laço de repetição em modo de software *pipelining*, as RPUs são configuradas para retirarem uma instrução que faz parte do laço e enviar o restante do pacote para próxima RPU. Esse procedimento deve ocorrer n vezes, em que n é a quantidade de instruções dentro do laço. Ao fim desse processo, cada RPU ficará com apenas uma única instrução (por padrão). Após retirar sua instrução e transmitir o restante do pacote, a RPU deve iniciar o processo de execução a quantidade de vezes definida no laço. Para a configuração das RPUs, a instrução LOOP é propagada junto com o resto do pacote. Para isso, cada RPU do caminho retira a instrução LOOP; decrementa o valor de n; retira a próxima instrução, que será a instrução a ser executada pelo laço; insere a instrução LOOP no pacote, com o n decrementado, e envia o pacote para a próxima RPU. A Figura 24 contém o algoritmo utilizado na implementação.

Figura 24 - Algoritmo de Execução do LOOP

```

1

instrucao = pop buffer()

se (instrucao = LOOP) entao

2

3

m = result 1 //quantidade de repetições

4

n = operandA //quatidade de instruções dentro do laço

5

prox instrucao <- pop buffer()</pre>

6

7

se (n > 0) entao

8

pacote loop <- monta pacote(loop, m, n)</pre>

9

push (pacote loop)

10

transmite()

11

fimse

12

enquanto (i < m) faca</pre>

13

executa (prox instrucao)

14

i++

15

fimenquanto

16

fimse

```

Além da alteração no simulador do IPNoSys, também foi necessária a adaptação no montador para que as instruções de LOOP sejam reconhecidas nos arquivos de código-fonte PDL.

Por questões arquiteturais apenas algumas instruções podem ser executadas em modo de software *pipelining*. São elas: as instruções lógicas e aritméticas (ADD, SUB, MULT, DIV, AND, OR, XOR, RSHIFT, LSHIFT e NOT), instruções de acesso a memória (LOAD e STORE) e as auxiliares (COPY e NOP). As demais instruções não têm escopo definido para execução dentro de um laço de repetição utilizando a instrução LOOP. Dessa forma, um compilador poderia identificar se as instruções contidas dentro do laço são compatíveis com a instrução LOOP, caso contrário implementaria o laço no formato original da arquitetura.

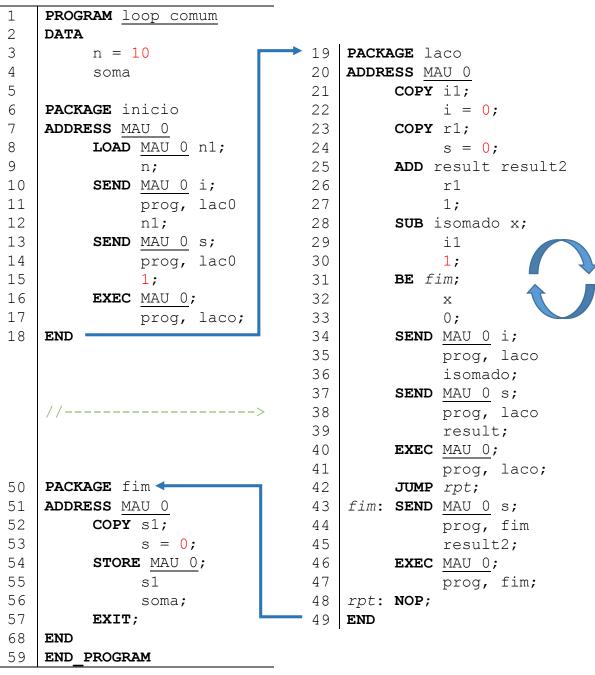

Para comparar o escopo do PDL, as Figura 25 e Figura 26 trazem, respectivamente, a implementação de um algoritmo de um contador simples para versão original da IPNoSys e para a versão IPNoSys SP<sup>2</sup>. A versão da IPNoSys original (Figura 25) contém os três pacotes necessários para criação do laço (Figura 18). O

<sup>&</sup>lt;sup>2</sup> Para simplificar a escrita, deste ponto em diante, a arquitetura proposta por esta dissertação será referenciada sempre por IPNoSys SP (software *pipelining*).

pacote "inicio" (linhas 6 a 18) inicializa o programa e chama o pacote "laco". O pacote "laco" (linhas 19 a 49) contém o código que será executado repetidamente e, em seguida, uma tomada de decisão para saber se o pacote deve executar de novo ou deve ser chamado o pacote "fim". O pacote "fim", por sua vez, guarda o resultado na memória e encerra o programa. É fácil notar que boa parte código é composto por instruções auxiliares necessárias ao controle do laço (SENDs e EXECs). O contador propriamente dito é restrito apenas a instrução ADD (linhas 25 a 27).

Figura 25 - PDL de um Laço de Repetição na IPNoSys Original

Fonte: Autoria Própria

Em contrapartida, a Figura 26 apresenta o PDL para o mesmo algoritmo, mas agora utilizando a instrução LOOP.

Figura 26 - PDL de um Laço de Rpetição na IPNoSys SP

```

PROGRAM loop SP

1

2

DATA

3

n = 10

4

soma

5

PACKAGE inicio

6

ADDRESS MAU 0

7

LOAD MAU 0 loop;

8

n;

9

LOOP 1 1;

10

loop;

11

ADD

s1 result;

12

s1 = 1

13

1;

14

STORE MAU 0;

15

result

16

soma;

17

EXIT;

18

END

19

END PROGRAM

```

Fonte: Autoria Própria

Enquanto o laço de repetição na IPNoSys original (Figura 25) necessitou de três pacotes e 59 linhas de código, a versão com SP (Figura 26) é escrita com apenas um pacote e 19 linhas de código. O contador, representado pela instrução ADD (linhas 11 a 13) irá executar a quantidade de vezes determinada pelo operando da instrução LOOP (linhas 9 e 10). Como não há mais necessidade de outros pacotes, as instruções de controle são dispensadas.

Para mostrar o passo-a-passo da instrução LOOP, a Figura 28 mostra um código em PDL para resolução do fatorial de um número qualquer. O PDL foi baseado no algoritmo de fatorial descrito na Figura 27. A versão utilizando o laço de repetição da IPNoSys original para o mesmo fatorial pode ser consultado no Apêndice A.

Figura 27 - Algoritmo de Fatorial

```

1

ALGORITMO fatorial

2

var

3

a, b, i, loop: inteiro

4

inicio

5

a < -5

b <- 1

6

7

loop < a - 1

8

para i de 1 ate loop faca

9

b <- b * i

10

fimpara

11

escreva(b)

12

fimalgoritmo

```

Figura 28 - PDL de um Fatorial

```

1

PROGRAM fatorial

2

DATA

3

a = 5 // valor que se deseja saber o fatorial

4